你好的支持团队。

我们在产品中使用 AM62x 处理器、存在以下问题。

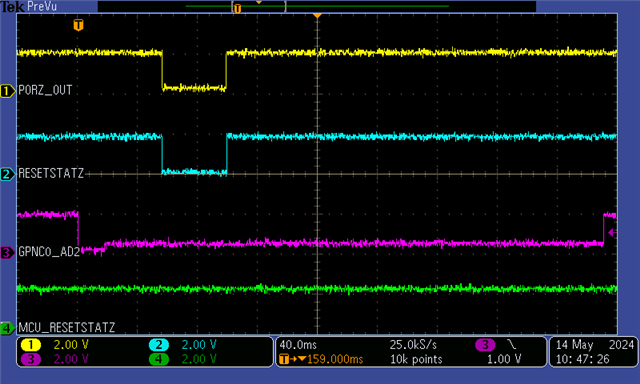

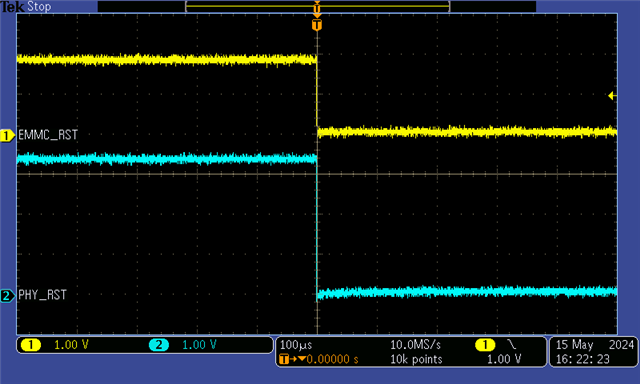

当 SoC 进入 DEEPSLEEP 模式时、SoC 的 RESETSTATz 输出被下拉、并将以太网 PHY、eMMC、DSI 至 LVSD 桥等外设器件置于复位状态。 当 SoC 从 DEEPSLEEP 模式返回到活动模式时、这种行为会在 SW 侧产生问题。

当 SoC 进入 DEEPSLEEP 模式时、是否有办法防止 RESETSTATz 引脚下拉?

或者、或许有一种方法可以指示 SoC 处于 DEEPSLEEP 模式? 例如、某些 GPIO 或电源轨可能已关闭。 当 SoC 进入 DEEPSLEEP 模式时、我可以使用该信号阻止向外设发送复位信号。

在我们的产品上、我们使用与 BeaglePlay 单板计算机(基于 AM62x SoC)类似的复位原理图。