工具与软件:

您好!

我使用mcu_plus_sdk_am64x_09_01_00_41并编写了代码来测量 GPIO 写入和读取次数。

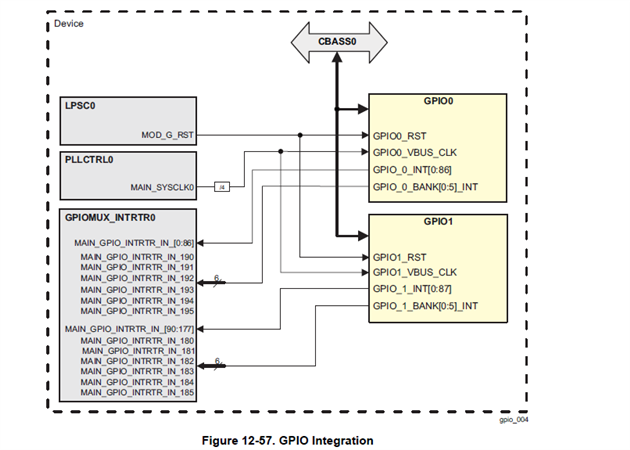

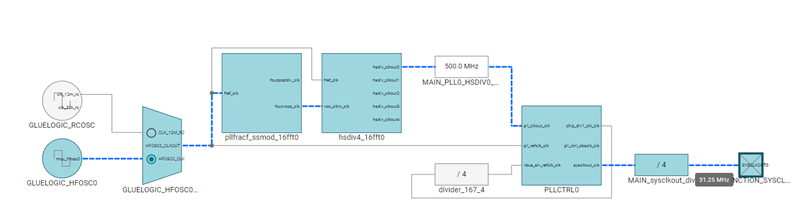

R5F 内核时钟设置为800 MHz、GPIO 外设时钟(GPIO0_VBUS_FICLK) 设置为125 MHz。

以下是刷写到 R5F 内核的代码。 在示波器上观察到波形:

gpioBaseAddr = (uint32_t) AddrTranslateP_getLocalAddr(GPIO_LED_BASE_ADDR);

pinNum = GPIO_LED_PIN;

GPIO_setDirMode(gpioBaseAddr, pinNum, GPIO_LED_DIR);

gpioBaseAddr1 = (uint32_t) AddrTranslateP_getLocalAddr(OUTPUT_GPIO_BASE_ADDR);

pinNum1 = OUTPUT_GPIO_PIN;

GPIO_setDirMode(gpioBaseAddr1, pinNum1, OUTPUT_GPIO_DIR);

uint32_t regIndex1, regVal1;

volatile CSL_GpioRegs* hGpio = (volatile CSL_GpioRegs*)((uintptr_t) gpioBaseAddr1);

regIndex1 = GPIO_GET_REG_INDEX(pinNum1);

regVal1 = GPIO_GET_BIT_MASK(pinNum1);

uint32_t regIndex, regVal;

volatile CSL_GpioRegs* hGpio1 = (volatile CSL_GpioRegs*)((uintptr_t) gpioBaseAddr);

regIndex = GPIO_GET_REG_INDEX(pinNum);

regVal = GPIO_GET_BIT_MASK(pinNum);

while(1)

{

CSL_REG32_WR(&hGpio->BANK_REGISTERS[regIndex1].SET_DATA, regVal1);

CSL_REG32_WR(&hGpio->BANK_REGISTERS[regIndex1].CLR_DATA, regVal1);

CSL_FEXTR(hGpio1->BANK_REGISTERS[regIndex].IN_DATA, regVal, regVal);

CSL_REG32_WR(&hGpio->BANK_REGISTERS[regIndex1].SET_DATA, regVal1);

CSL_REG32_WR(&hGpio->BANK_REGISTERS[regIndex1].CLR_DATA, regVal1);

}

从波形中、我们观察到了以下时序:

- GPIO 高电平时间:~210ns

- GPIO 低电平时间:~210ns

- GPIO 读取时间:~210ns

您能否确认这些时间是否正确?

此外、我想知道是否可以将 GPIO 外设时钟频率增加到超过125 MHz 以实现低于210ns 的时间。 如果可以提高外设时钟频率、更改该频率的步骤是什么?

我们是否能够将 PLL0_hsdiv0值增加至超过500MHz 的值? 允许的 PLL0_hsdiv0的最大值是多少?

谢谢!

Pratibha