主题中讨论的其他器件:AM623、 AM6546、 AM6442、 AM2432、 TDA4VH-Q1、 TDA4VH

工具与软件:

尊敬的 TI 专家:

我对 SOC POK 模块类型的电压监控功能、精度、设计建议和支持的电源轨有疑问。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的电路板设计人员:

请参阅以下 POK 模块说明。

电源正常(POK)模块

POK 模块负责准确检测电压电平。 每个模块都进行了调整以考虑在内

温度变化时、效率是如何变化的。

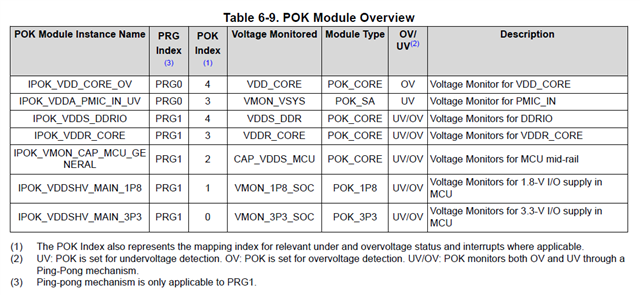

该系列器件实现了两种类型的 POK 模块- POK 和 POK_SA。 请参阅关于的表6-9

POK 的类型及其监控的电压。

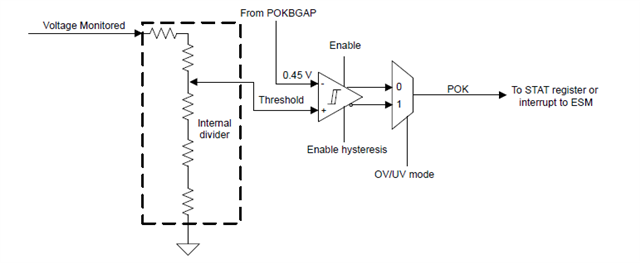

POK 方框图

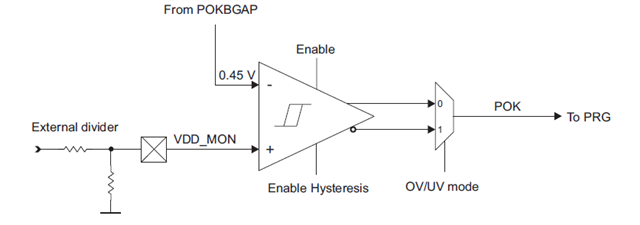

POK_SA 方框图

此致、

Sreenivasa

尊敬的电路板设计人员:

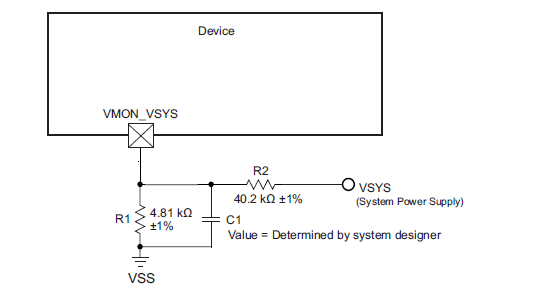

请参阅以下指南来了解 VMON_VSYS 分压器的实现

系统电源监测设计指南

建议使用 VMON_VSYS 实现电压监控功能 、以便及早检测电源故障。 这将成为 进入 PCB 的主输入(较高)电压轨的电源故障指示器。 例如5伏、12伏或24伏。

与此监控器相关的误差需要您将阈值设置为 明显低于标称值、以避免误触发

请参阅 处理器特定数据表的系统电源监测设计指南一节

系统电源监测分压器电路

问:当我们查看数据表中的说明时、 其中指出、如果 VMON_VSYS 引脚电压降至0.45V 以下、则会触发电源故障事件。 当出现该触发信号时会发生什么情况?

当施加到 VMON_VSYS 的电压 降至内部参考电压以下时、它会触发一个路由到 ESM 的中断。 处理 POST ESM 中断由软件配置、范围可以从中断内核到复位器件。

此致、

Sreenivasa

尊敬的电路板设计人员:

请参阅以下指南来监控 CAP_VDDS_MCU

用例:

我们想调整 CAP_VDDS_MCU 监控器的电压范围。

根据 TRM、我们 为选择了以下修整值

POK_VMON_CAP_MCU_GENERAL_UV = 2Eh = 0101110b = 1.728V

POK_VMON_CAP_MCU_GENERAL_OV = 22h = 0100010b = 1.888V

尽管 IO 电源正确、但我们通过这些设置获得 UV 中断。

默认值似乎为(我们在写入寄存器之前先对其进行读取):

POK_VMON_CAP_MCU_GENERAL_UV = 23h = 0100011b = 1.502V

POK_VMON_CAP_MCU_GENERAL_OV = 1Dh = 00111101b = 1781V

好的、现在我想我知道发生了什么。 在我看来、他们认为该 VMON 监控的是1.8V 电源、但实际上、该 VMON 连接到 CAP_VDDS_MCU、而不监控1.8V 阈值。

它不是固定电压。 当相应的 VDDSHV 在1.8V 下运行时、该引脚应具有与 VDDSHV 电源相同的电位。 当相应的 VDDSHV 在3.3V 下运行时、它应该具有跟踪到 VDDSHV 源½ Ω 的电势。

我们没有在数据表中公布这些引脚上的电压、因为我们从未期望任何连接到这些引脚。 我最近才了解到其中一个 LDO 输出与 POK 输入具有内部连接。

当 VDDSHV 斜升至3.3V 时、LDO 输出将跟踪 VDDSHV、直到其达到大约2.4V。 此时、辅助电源电路从我所说的开关模式变为 LDO 模式。 此时、它开始跟踪½ VDDSHV。 我怀疑输出电容将保持2.4V 电势一段时间、然后 IO 偏置电路会汲取足够的电流、使电容放电回到½ VDDSHV 电位。

随着 VDDSHV 衰减、我预计会发生类似的情况。 当 VDDSHV 降至2.4V 以下时、辅助电源电路将切换回开关模式、此时 VDDSHV 的电势将施加到电容器上。

我认为这不会给 POK 配置带来问题、因为它只会在 IO 电源稳定后进行配置。 这主要是在选择具有合适额定电压的电容器时需要考虑的问题。 这就是我们更新到信号说明注释以包含电容器额定电压的原因。

此致、

Sreenivasa

尊敬的电路板设计人员:

有关 POK 阈值设置、请参阅以下指南

阈值设置用例

问:IPOK_VDDSHV_MAIN_3P3 UV 限制默认为3.015V、但数据表中建议的最小值为3.135V。 电压可能低于 ROC、但 POK 仍无法检测到它。

VMON_1P8_SOC 和 VDDR_CORE 也是如此、它们都不依赖于电源架构(根据设计确定)。

这并不是一个错误 POK 的默认范围比建议的运行条件更宽、因为这是中的建议

POK 规格–为 POK 元件变化留出容差

POK 精度3%的总容差+ 1%的保护频带是规范具有的值。

如果客户需要、可以将其拉入、但需要更严格地进行供电、否则会有误触发的风险。

此致、

Sreenivasa

尊敬的电路板设计人员:

关于 CAP_VDDSx 值的建议

LDO 规格 为0.8uF 至1.5uF。 考虑到偏置、随着时间的推移而下降等因素、电容器应在该范围内

问:在6.3V/10V 的情况下、选择 X7R 电容器后、考虑到直流效应和其他降级、电容值可能会降至0.7uF。 较高的电容值可能需要使用0402电容、这可能会影响布局。

电容是否取决于用于特定 IO 电源轨的 IO 数量和 IO 拉电流/灌电流 、或者无论使用何种 IO、都需要该电容。

https://www.kyocera-avx.com/docs/techinfo/CeramicCapacitors/mlcc-dc-bias-characteristics.pdf

CAP 值与 IO 计数和活动无关。 为了确保 LDO 的稳定性、需要产生辅助电源。 任何超出此额定范围的值都可能导致偏置发生器不稳定、从而导致过压应力。

附加指南

选择 ESR 小于1欧姆的电容器

确保 PCB 环路电感< 2.5nH

选择0201封装

请参阅 SoC 数据表

此致、

Sreenivasa

尊敬的电路板设计人员:

软件中的 VMON_VSYS 引脚监控

软件是否能够读回在 VMON_VSYS 引脚上检测到的电压?

我们在当前设计中将5V 电压轨馈入 VMON_VSYS 引脚、并且想要读回电压感测。

TRM 第5.2.2.1.1章"电源正常(POK)模块"中记录了电源监控。

POK 在 Linux 中不使用,因此我将把您的查询发送给我们的硬件专家,以了解详细信息。

我们在当前设计中将5V 电压轨馈入 VMON_VSYS 引脚、并且想要读回电压感测。

请注意、这是一个比较器输出。

这意味着我们会先从 Sitara 读回输出端0或1、 正确。

此致、

Sreenivasa