工具与软件:

`您好、TI 的团队:

我们正在寻找在 PC 仿真模式下如何控制 ISP 参数、如 AWB 增益等。 (x86平台)

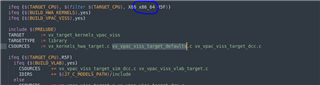

我们看到配置默认值应用在头文件"vx_vpac_viss_target_defaults.c"中。

我们的查询如下:

1.如果修改此报头中的内容,会在执行 PC 仿真时反映出来。

如果不是、是否还有其他方法可以实现?

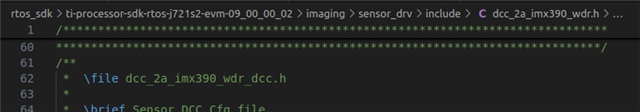

2.我们可以用配置文件中的一些更改来重新编译 DCC-bins。 但看起来更改在 PC 仿真执行期间没有得到反映。

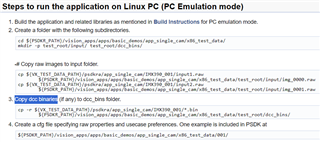

我们将按如下方式应对更新后的 DCC-Bins:

如果我错了,请纠正我。