工具与软件:

尊敬的 专家:

我们已经完成了 MCU+SDK 为 DCC 提供的代码。

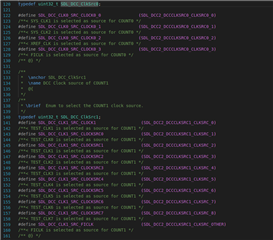

我们在 DCC_309a Test_Use 中做了一些更改

/*连续-未生成错误*/

{

"HFOSC0"、

"SYSCLK0"、

SDL_DCC_INST_DCC1 、

// SDL_DCC_INST_MCU_DCC0、

SDL_DCC_CLK0_SRC_CLOCK0_0、

25000、/* HFOSC0的25 MHz */

SDL_DCC_CLK1_SRC_CLOCK1、

200000、/* 200 MHz for SYSCLK0 */

SDL_DCC_MODE_CONTINUOUS、

0x0、

APP_DCC_TEST_CLOCK_SRC_1_Higher、

0x0

}、

我将实例更改为 SDL_DCC_INST_DCC1 来自 SDL_DCC_INST_MCU_DCC0、之后、它似乎变得失败、时钟不匹配或漂移。

------------ before chages ------- MCU_R5FSS0_0] DCC Example Test Application DCC_Test_init: Init WKUP ESM complete USECASE: 0 Source clock: HFOSC0 Test clock: SYSCLK0 SDL DCC EXAMPLE TEST: Seed values calculation done. SDL DCC EXAMPLE TEST: Enabling DCC and running for some time UC-0 count:0 Completed Successfully All tests have passed. --------------After chages --------------- [MCU_R5FSS0_0] DCC Example Test Application DCC_Test_init: Init WKUP ESM complete USECASE: 0 Source clock: HFOSC0 Test clock: SYSCLK0 SDL DCC EXAMPLE TEST: Seed values calculation done. SDL DCC EXAMPLE TEST: Enabling DCC and running for some time SDL DCC EXAMPLE TEST: DCC Generated Error interrupt SDL DCC EXAMPLE TEST: Indicating clock drift/change SDL DCC EXAMPLE TEST: Error Event was not expected UC-0 Failed Few/all tests Failed

我想知道更多关于这个源时钟,参考时钟和这些实例. 您能告诉我们应该遵循什么吗?

此致、

去巴希