Thread 中讨论的其他器件:SYSBIOS

工具与软件:

你(们)好

这种情况仅发生在 C66上、A15上也是如此。

BIOS_6_52_00_12

谢谢

Raste.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Rasty、

要设置正确的预期目标、请注意我们的 SYSBIOS 支持非常有限。

尽管如此、这看起来并不正确、而且肯定不是应该发生的事情。 (当然、您已经了解了这一点。)

在你共享的.cfg 文件中、我看不出你正在使用什么样的信标、 你能够共享正在使用什么样的信标吗?

较低优先级的线程是否有可能禁用调度程序? 即调用 Task_disable() ?

事件组合器模块的作用是什么?

-若苏厄

您好!

我们使用从 ISR 释放并由高优先级任务执行的信标。

我们不使用 Task_disable()。

您可以通过在低优先级运行以下代码来轻松重现此行为:

while (1)

{

volatile int i = 1000000;

while (i --)

{

}

睡眠(100);<-在此处输入断点、您将看到高优先级任务处于"就绪"状态。

}

而无需任何信标或 Task_disable。

我可以给你一个提示:

cfg 文件中的以下2行

var BIOS = xdc.useModule('ti.sysbios.BIOS');

BIOS.swiEnabled = false;

修正此行为、但具有非常奇怪的副作用。 也许这将为您提供一些方向。

谢谢

Raste.

你(们)好

这个项目已经运行了几年。

将某些功能(计算)从 A15卸载到 C66。

从第1天开始、它就在我们的路线图上、但由于项目计划而延迟了。

我们制定了 C66和 POC 的所有基准并认为它可以接受。

就在发布前几天、我们发现从低优先级任务到高优先级任务存在干扰。

您需要了解以下内容。

1.由 GPIO 触发的周期性 ISR。 工作正常。

2. ISR 向高优先级线程发送一个二进制信标。 工作正常。

3.线程唤醒并做一些有用的工作,并再次挂起信标。 工作正常。

4.低优先级任务(如下图所示)对高优先级线程产生干扰。 这不是我所期望的。

应用非常简单、此外我们还有简单的诊断控制台连接到 UART。

个性签名 不会

1.阻止中断

2.暂停调度程序

3.使用可导致优先级反转的互斥体。

正如您在初始帖子中的图片所示

低优先级任务"正在运行"、而高优先级任务"就绪"、 这是异常情况、我不会期望抢先式实时内核。

此致

Raste.

while (1)

{

volatile int i = 1000000;

while (i --)

{

}

睡眠(100);<-在此处输入断点、您将看到高优先级任务处于"就绪"状态。

}

Rasty、

请参阅 TI-RTOS 内核用户指南:信标的第4.1章

低优先级的任务"正在运行"、而高优先级的任务"就绪"、 这是一种异常现象、我不会期望抢先式实时内核能做到这一点。

对、您有三个使用一个二进制信标的任务。 这是我的初始诊断。

请访问 https://focus.ti.com/download/trng/multimedia/dsp/OLT110026/semaphores.mp4

此致!

若苏厄

这 不是我写的。

周期 ISR 发布一个二进制信标给在信标上挂起的任务(为清楚起见、我们删除了第二个周期任务)。

周期性任务应完成其工作、直到下一次中断。

有一个低优先级任务根本不使用任何信标、只有紧密循环和睡眠。

因此、我们有一(1)个中断、一(1)个高优先级周期性任务、一(1)个信号量(在 ISR 和高优先级周期性任务之间)和一个低优先级任务 根本不使用任何信标 .

由于低优先级任务、高优先级任务会延迟。

同样的情况在 A15上可以正常工作、但在 C66上不可行。

我使用不同类型的 RTOS ,如 VxWorks,FreeRTOS,TheadX,SYS-BIOS , 20年的发展经验。 我知道信标的工作方式以及预期结果。

Rasty、

我根据您所写的"线程(s)"(复数)假设:

。 ISR 向高优先级线程发布一个二进制信标。 工作正常。

如果这是一个错误的假设,我很抱歉,只是试图帮助。

下面列出了其他一些想法:

您能否在一个 TI 电路板的小示例中重新创建该设计并将其与我们分享以进行测试?

-若苏厄

我希望这一问题已为人所知、您可能已经有了一些解决方案。

我们将 对这个问题进行简单的独立复制并上传。

我有几个问题。

1. SYS BIOS 是否有可以打开/关闭的非抢先式模式?

2.是否可以在 C66 ISR 中使用浮点? 我们应该怎么做才能在 ISR 中启用浮点?

3.对于从 ISR 发送消息(通过消息队列)是否有任何限制? 例如不同的 API/等?

谢谢

Raste.

Rasty、

我今天不在办公室,我下周会回来。 您可以在 https://software-dl.ti.com/lprf/simplelink_cc26x2_latest/docs/tirtos/sysbios/docs/Bios_User_Guide .pdf 上找到许多此类信息

此致!

若苏厄

Rasty、

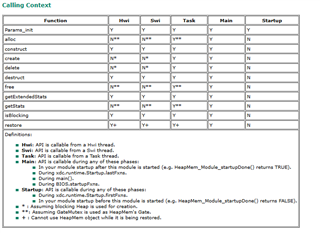

这些章节包括 ISR 的限制:

如需了解更多相关信息、请访问:

以及回顾:

另一个限制是应避免在 HWI 或 SWI 上下文中进行内存分配。

-若苏厄