请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM6442 主题中讨论的其他器件:SysConfig

工具与软件:

具有功能 PCIe 设置、AM64x 在 A53上运行 Linux (作为根复合体)和 FPGA 板(作为端点)。 通过 AM64x (RC)、我可以成功检测到 FPGA (EP)并对寄存器和条形存储器执行读取/写入操作。

根据所讨论和并参考 TMDS243EVM:PCIE:RC 读取 EP 条信息卡滞。 243EVM+Intel FPGA -基于 Arm 的微控制器论坛-基于 Arm 的微控制器- TI E2E 支持论坛、我按照下面的建议步骤操作。 ‘、该问题仍然存在、即"PCIe 链路未建立、LTSSM 仍处于0x00 (检测)状态"。

- FPGA 板直接插入 AM64x PCIe 连接器。

- 按照 AM64x MCU+ SDK:PCIe 缓冲区传输 RC 示例进行操作。

- 移除 AM64x 上的跳线 J34。

- 还‘在"AM64x (RC) PCIe 连接器(A 侧引脚13和14)"和 FPGA (EP)上的示波器验证了 PCIe REFCLK。 它由 RC 和 EP 的100MHz 提供。

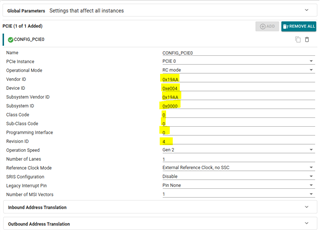

下图分别显示了使用 SysConfig 的 FPGA 中的 PCIe IP 和 AM64x R5中的 PCIe 外设配置。 请回顾这些建议、如果正确、请告诉我。

对于作为根复合体的 AM64x、突出显示的参数是设置为"端点"配置值还是本地根复合体配置值?