主题中讨论的其他器件:TDA4VM

工具与软件:

有关采用 DDR MT53E512M32D1ZW-046 AUT:B 培训的 TDA4VM 的问题:

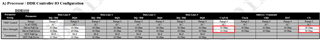

1.内部 DDR 寄存器 MR11、MR12、MR14和 MR22通过哪个寄存器配置 TDA4VM? TDA4VM 的 DDRSS_CTL_179是否会修改 DDR 的内部 MR12寄存器?

2.何时分别执行 TDA4VM 的命令总线训练、读 DQ 训练和写训练? 当环境温度变化时、TDA4VM 是否会自动进行 DDR 训练? 动态调整的刷新率是否与 DDR 培训相关?

3.在命令总线训练、读取 DQ 训练和写入训练后,是否会更新 DDR 中的 MR11、MR12、MR14和 MR22寄存器?

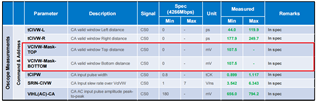

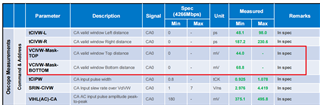

4.在 jacinto7 DDRSS regconfig 工具中、在 DRAM IO 配置中配置 MR12寄存器 CA VREF 25.6%(对应于 DDR 数据表中的0x12)。

然而、工具生成的代码 DDRSS_CTL_179为0x27270056、相应的百分比0x27为38.3%、这与 DDR 数据表不对应。 如何转换工具生成的值以及 DDR 数据表中的值?

5.我们测量了不同的电路板、且在启动后和启动一段时间后、DDRSS_CTL_179的读数始终为0x270056。 在温度发生变化(85°C 到-40°C)后、该值也保持不变、在低温重启后、该值也保持不变。 DDR 何时进行培训?

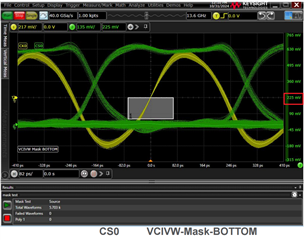

6.当 Micron 实验室帮助我们测试信号完整性时,他们报告我们提供的 MR12和 MR14不准确,他们最终使用的 CA VREF 为20.5%,而 DQ VREF 为21.5%。 且测试通过。

7.我们有一个在低温(-40℃)下运行一段时间(如2小时)后异常重启的电路板,在室温下是正常的。 我可以问如何捕获日志来帮助确定重启是否是由异常 DDR 引起的吗? 在重新启动之前、UART 接口捕获的当前日志未更改。