主题中讨论的其他器件:SysConfig

工具与软件:

您好!

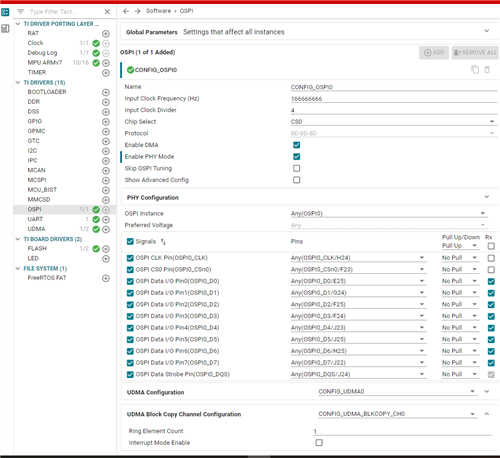

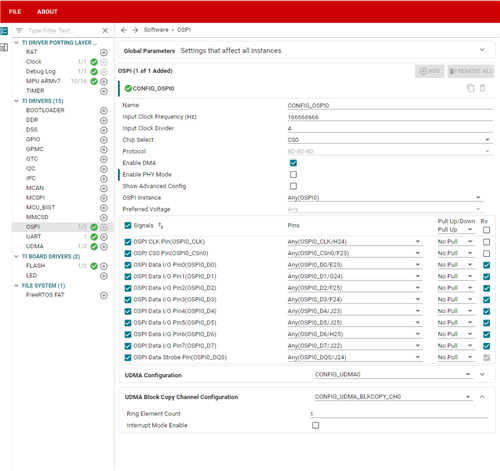

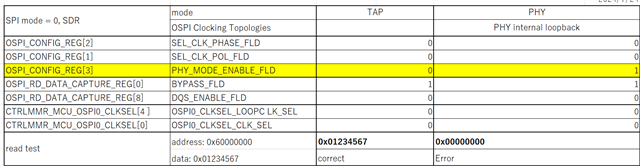

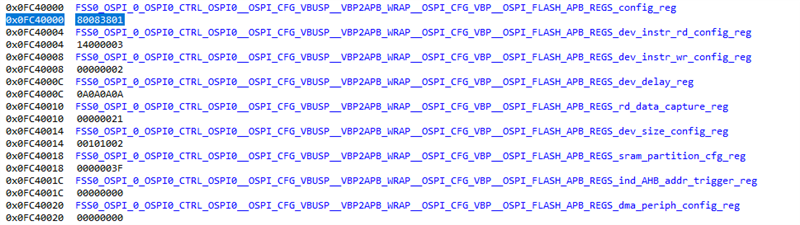

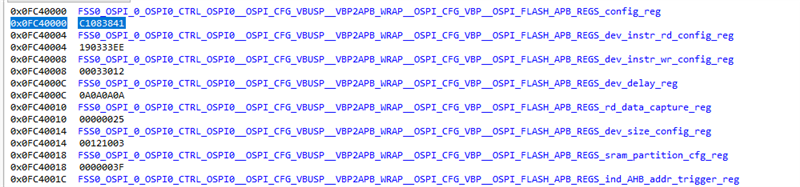

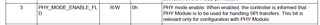

我的客户希望使用具有内部 PHY 环回的 QSPI PHY 模式。

根据原始线程中的表支持此模式。 我在下面复制了它。

| 以太网 PHY | 点击 | |||||

| SDR | DDR | SDR | DDR | |||

| 基准时钟 | 和数据训练 | 无数据训练 | 和数据训练 | 无数据训练 | ||

| 无环回 | 不适用 | 不适用 | 不适用 | 不适用 | 50MHz (表7-122) | 25MHz (表7-124) |

| 内部 PHY 环回 | 不支持 | 166MHz 或142MHz (表7-116、7-117) | 不支持 | 不支持 | 不适用 | 不适用 |

| 内部焊盘环回 | 不支持 | 不支持 | 不支持 | 不支持 | 不适用 | 不适用 |

| 外部电路板环回 | 不支持 | 166MHz 或142MHz (表7-116、7-117) | 不支持 | 52MHz (表7-119、7-120) | 不适用 | 不适用 |

| DQS | 不支持 | 不支持 | 166MHz 或132MHz (表7-113、7-114) | 52MHz (表7-119、7-120) | 不适用 | 不适用 |

您能告诉我如何配置 QSPI 寄存器以启用该模式吗?

谢谢。此致、

田代浩一郎