工具与软件:

尊敬的 TI:

如何 在 csitx RTOS 驱动程序中修改 dphy_TxByteClkhs_cl_clk 和 vbus_clk_clk? 我们使用了 pdk_j721s2_10_00_00_27

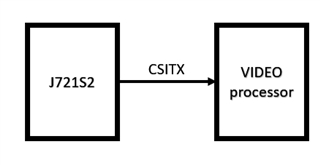

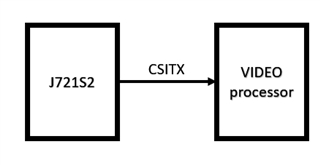

目前,我们将视频 处理器连接在 J721S2 CSITX 输出之后,并将 CSI 转换为 并行。

如果 dphy_TxByteClkHS_cl_clk 和 VBUS_clk_clk 发生更改、视频处理器供应商希望测试视频处理器会出现什么情况。

—— 谢谢。 此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的 TI:

如何 在 csitx RTOS 驱动程序中修改 dphy_TxByteClkhs_cl_clk 和 vbus_clk_clk? 我们使用了 pdk_j721s2_10_00_00_27

目前,我们将视频 处理器连接在 J721S2 CSITX 输出之后,并将 CSI 转换为 并行。

如果 dphy_TxByteClkHS_cl_clk 和 VBUS_clk_clk 发生更改、视频处理器供应商希望测试视频处理器会出现什么情况。

—— 谢谢。 此致。

您好、 Brijesh:

我很难描述该处理器的工作原理。

无论是降低通道速度还是降低 通道数、 视频处理器输入像素时钟参数也需要调整为250MHz 以锁定 帧。

视频处理器供应商认为 dphy_TxByteClkhs_cl_clk 和 vbus_clk_clk 的设置过高、视频处理器供应商 希望尝试降低频率。

你可以帮我,并与我讨论如何 修改? 请...

—— 谢谢。 此致。

现在、我们有一些问题。

如果我们 使用 CSI RX 转 CSI TX 示例、则 J721s2 CSI TX 会按每帧稳定输出33ms、并且视频处理器可以正常锁定每个帧。

如果我们 将 vxProcessGraph 用于 CSI TX、则 J721s2 CSI TX 会每帧输出非稳定的33ms (约27ms~33ms、从示波器测量、视频活动数据 是固定时间、消隐时间不是固定值。)

如以下主题:

您好、 Brijesh:

感谢您的答复。

如果我们更改了 laneSpeedMbps 、是否还有其他参数需要修改?

dphyCfg->laneSpeedMbps = 477

dphyCfg->psmClkFreqDiv = CSITX_DPHY_PSM_CLK_FREQ_DIV_DEF;

dphyCfg->pllByteClkDiv = CSITX_DPHY_PLL_BYTE_CLK_DIV_DEF;

dphyCfg->pwmCtrlDivLow = CSITX_DPHY_PWM_CTRL_DIV_LOW_DEF;

dphyCfg->pwmCtrlDivHigh = CSITX_DPHY_PWM_CTRL_DIV_HIGH_DEF;

dphyCfg->pllLockThreshold = CSITX_DPHY_PLL_LOCK_THRESHOLD_DEF;

dphyCfg->pllLockStart = CSITX_DPHY_PLL_LOCK_START_DEF;

dphyCfg->pllIpDiv = CSITX_DPHY_PLL_IPDIV_DEF;

dphyCfg->pllOpDiv = CSITX_DPHY_PLL_OPDIV_DEF;

dphyCfg->pllFbDiv = CSITX_DPHY_PLL_FBDIV_DEF;

dphyCfg->pllPd = CSITX_DPHY_PLL_PD_DEF;

dphyCfg->waitBurstTime = CSITX_DPHY_WAIT_BURSTTIME_DEF;

dphyCfg->txClkExitTime = CSITX_DPHY_TX_CLK_EXITTIME_DEF;

dphyCfg->dlWkupTime = CSITX_DPHY_DL_WKUPTIME_DEF;

dphyCfg->clWkupTime = CSITX_DPHY_CL_WKUPTIME_DEF;

dphyCfg->clSlewRateCtrl = CSITX_DPHY_SLEWRATECTRL_DEF;

dphyCfg->dlSlewRateCtrl = CSITX_DPHY_SLEWRATECTRL_DEF;

您好、 Brijesh:

如何确保帧每33.3ms 提交一次?

请在 以下主题中提供您的方法:

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1429324/tda4vm-is-blanking-config-of-csitx-node-work

—— 谢谢。 此致。

您好、 Brijesh:

我们在 csitx 驱动程序中看到了对垂直消隐时间的描述、如下所示:

消隐时间是以像素还是行计算的???

pdk_j721s2_10_00_00_27\packages\ti\drv\csitx\include\csitx_cfg.h

/**\short 垂直消隐:默认 VB (以像素数表示)

*用于初始化*/

#define CSITX_IN_FRAME_VB_DEFAULT (0U)

—— 谢谢。 此致。

Terry、您好!

与 所需的总速度相比、您的车道速度是否设置为高值? 就像您将其设置为1.5Gbps 一样、4通道输出的总速度将为6Gpbs、而如果您只是以30fps 的速率发送1920x1080 YUV422输出、它只需要大约1Gbps 的总速度(1920x1080x30x16)。 您只使用了总 BW 的16%、在本例中、 每33.3ms 发送帧的唯一方法是使用计时器。 在每次计时器回调时、请将帧提交到 CSITX 驱动程序。

BTW、哪个组件馈送到 CSITX? 它最终是否连接到 CSIRX?

此致、

Brijesh

您好、 Brijesh:

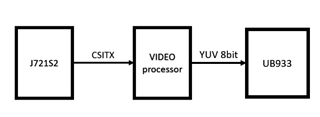

我的 CSI TX 参数如下所示:

H 激活:1280 像素

V ACTIVE:960 线

H blank:310 像素

v 空白:290 行

通道速度:477Mbps

2 通道

(1280+310)*(960+290)* 2*30*8/2=477Mbps

哪个组件正在馈送至 CSITX? 它最终是否连接到 CSIRX?<=== 您是指我们的视频芯片在硬件中所用的东西吗?

—— 谢谢。 此致。