- 你(们)好。

- 1、目前、我们计划使用 AM4372BZDNA60和 FPGA 构建硬件系统。

使用 CPU 的 GPMC 接口(AM4372)连接到 NOR 闪存、并在非地址数据线路多路复用模式下与 FPGA 进行通信、最大数据位为16位。

使用 GPMC 的 DMA 传输发送8个数据、每个4字节。 采用8个 DMA 通道进行传输、这种方案是否可行? - 2、DMA 的最大数据传输速度是多少? 每个通道的最大 FIFO 缓冲区是多少? DMA 可以访问的最大内存是多少? 512KB?

- 谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Sheng:

首先、我是 Linux 采购员、基本上擅长讨论 DMA 在内核器件驱动程序中的用法、但我不知道所有的 EDMA 模块内部。

在 EDMA 中、有64个与64个通道一对一对应的直接映射事件。 每个事件只能使用固定通道、这意味着即使特定事件未发生、分配给该事件的通道也无法被其他事件使用。 这是正确的理解吗?

是的、大多数 DMA 通道都一对一映射到特定的源模块、如 TRM 表11-24和11-25中所示。 但这些表格还列出了一些具有"开放"源代码模块的通道、这意味着这些通道可以映射到不同的源代码模块。

如何确认 DMA 传输速度? [报价]DMA 吞吐量在很大程度上取决于数据包大小。 例如、从 MMC 进行传输时的传输速度与从 UART 进行传输时的传输速度将大不相同。 我在 Linux 中没有 DMA 吞吐量报告、但我相信从 GPMC 传输时 DMA 不会成为瓶颈、我认为 GPMC 上的最大时钟是100MHz。

您好、 Bin Liu

感谢您的答复。

我目前的要求是从以前的产品过渡、以前的产品使用集成了 CPU 和 FPGA 的 SOC、内部 FPGA 通过 DMA 将数据传输到 CPU。 我现在打算切换到 AM437x+FPGA 模式。 当前计划是通过 GPMC 接口连接 AM437x 和 FPGA、AM437x 在内部通过 DMA 将数据传输到 DDR。

我在技术手册中发现、GPMC 接口的最大时钟是100MHz、并且 GPMC 带宽应满足要求。 但是、手册指出 TPCC 和 TPTC 的最大时钟是200MHz。 我是否需要专门关注 DMA 传输速度、或者它是否足以确认 GPMC 接口的速度? 使用 DMA 时的最大缓冲区大小是多少?

是否有任何适用于 GPMC DMA 配置的技术文档?

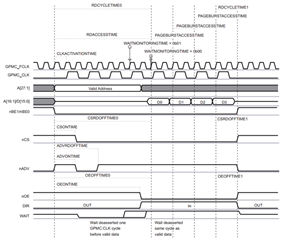

如下图所示。 如果我们考虑地址位的读取时间并在 GPMC 的100MHz 最大频率下运行、GPMC 可以实现的最大带宽是多少?

您好、Sheng:

我需要特别关注 DMA 传输速度、还是足以确认 GPMC 接口的速度? [报价]我曾尝试找到 EDMA 性能报告、但没有找到。 不过、我认为您不需要担心 GPMC 接口上的 EDMA 性能。 EDMA 用于整个 AM437x 系统、包括将数据从 DDR 传输到 DDR、这应该比 GPMC 快得多。

使用 DMA 时的最大缓冲区大小是多少?AM437x DMA 可进行3D 传输、每个维度高达64K。 因此、最大缓冲区大小将为64K*64K*64K。

[quote userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5514699 GPMC 可达到的最大100MHz 带宽是多少?[/quote]我会将您的问题发送给我们的 GPMC 专家以征求您的意见。

您好、 Bin Liu

感谢您的答复。

我刚刚了解到 CPU 所需的软件操作系统是 NORTI。

AM43XX 系列 GPMC 接口的最大时钟为100MHz、最大数据宽度为16位、从而使数据带宽为100MHz x 2字节= 200MB/s 我是这样计算的。 此计算正确吗?

目前、需要将 LCD 显示数据从 CPU 传输到 FPGA。 根据不同屏幕分辨率的数据大小、VGA 约为100MB/s、SVGA 约为150MB/s、XGA 约为250MB/s

GPMC 的带宽可能不满足要求。

除了使用 GPMC 接口连接 FPGA 外、AM43XX 系列还能否通过其他接口连接 FPGA?

您好、Sheng:

[报价 userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5517197 #5517197"] AM43XX 系列 GPMC 接口的最大时钟频率为100MHz、最大数据宽度为16位、由此产生的数据带宽为100MHz x 2字节= 200MB/s 我是这样计算的。 此计算是否正确?[/QUOT]这大致正确。

GPMC 的带宽可能无法满足要求。

除了通过 GPMC 接口连接 FPGA 外、AM43XX 系列还能通过其他接口连接 FPGA 吗?

我想不出任何其他解决方案,但我正在将您的查询发送给我们的硬件专家以征求意见。

您好、Sheng:

[报价 userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5522552 #552252"]1、您是否建议 CPU 通过 DSS 接口连接到 LCD 屏幕、而不是使用 FPGA 连接到 LCD 屏幕?有。

[报价 userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5522552 #552252"]2、在 CPU+FPGA 系统设计中为 CPU 和 FPGA 使用共享 DDR 是否可行?FPGA 如何共享 DDR? FPGA 是否能够直接访问 DDR?

您好、 Bin Liu

由于使用 GPMC 接口的带宽可能不足、有必要考虑两种替代解决方案:

您能帮我确认解决方案2吗? 谢谢你。

您好、 Bin Liu

1024x768的帧速率为60Hz。

我目前需要查看 DSS 界面以确认是否可以执行覆盖显示。 目前所需的覆层数为5层。

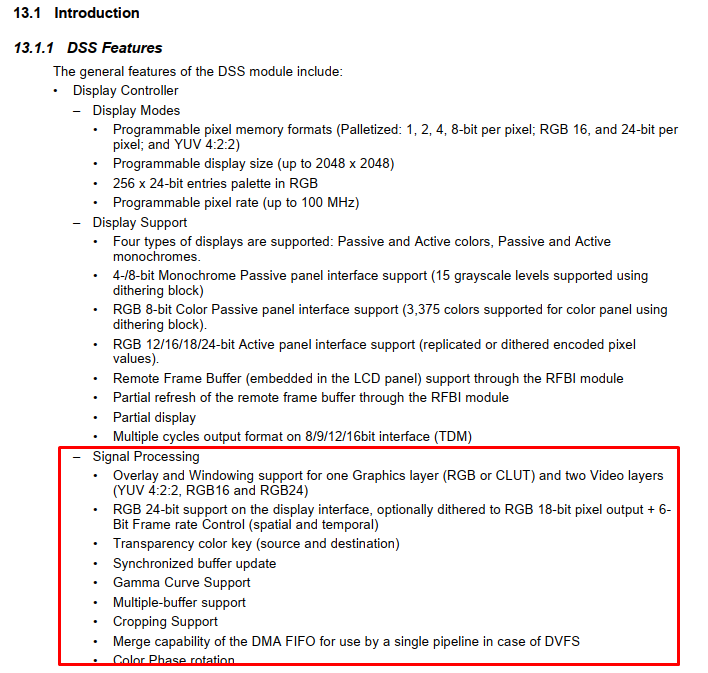

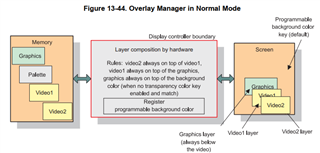

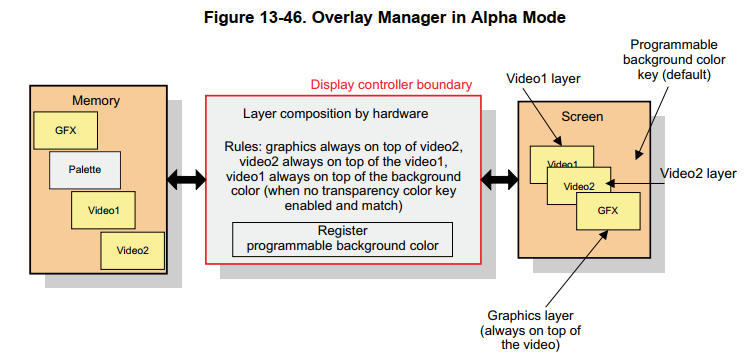

下图红色框中的说明是否表明 AM437x 只能实现两层重叠?

对一个图形层(RGB 或 CLUT)和两个视频层的覆盖和窗口化支持

(YUV 4:2:2、RGB16和 RGB24) 如何理解这句话?

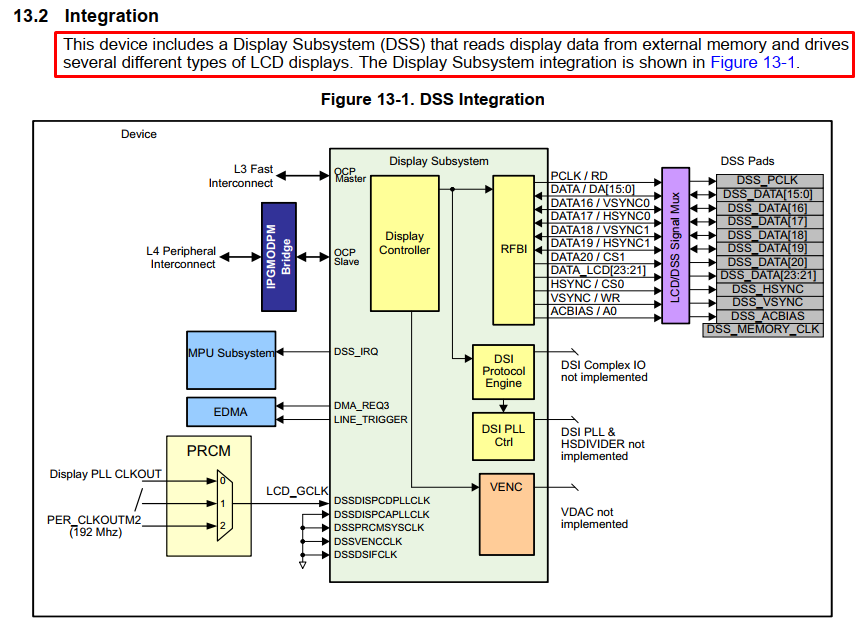

如何理解这句话? DSS 从外部存储器读取显示数据并驱动各种类型的 LCD 显示屏。

LCD 控制器输出的并行旁路模式和 RFBI 模式之间的区别是什么? 由于我需要24位输出、因此无法使用 RFBI 模式。 在旁路模式下、是否仍可以执行分层操作?

您好、Sheng:

[报价 userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5524786 #5524786"]下图红色框中的说明是否表明 AM437x 只能实现两层重叠?

对一个图形层(RGB 或 CLUT)和两个视频层的覆盖和窗口化支持

(YUV 4:2:2、RGB16和 RGB24) 如何理解这句话?

是的、一个 gfx 层加上两个视频支付器、总共3层。

您好、 Bin Liu

1、"一个图形层(RGB 或 CLUT)和两个视频层(YUV 4:2:2、RGB16和 RGB24)之间有何区别? 这些图形和视频层是否并排存在?"

2、"我已经审阅了操作手册的内容,似乎 GPMC 功能和 DSS 功能不能一起使用,因为它们共享许多只能支持一种功能的多路复用引脚。 不过、我需要使用 CPU 驱动 LCD 屏幕、同时还使用 GPMC 接口连接到 FPGA 以进行数据交互。 "这可能无法实现。

目前、需要将 LCD 显示数据从 CPU 传输到 FPGA。 根据不同屏幕分辨率的数据大小、VGA 约为100MB/s、SVGA 约为150MB/s、XGA 约为250MB/s。

这难道不是意味着 CPU 将 LCD 显示数据传输到 FPGA、然后 FPGA 将数据驱动到 LCD?

这就是为什么我建议使用 AM437x DSS 接口而不是 GPMC。

您好、 Bin Liu

1、不能并排。 全部3个层都重叠。

是否有任何与一个图形层(RGB 或 CLUT)和两个视频层(YUV 4:2:2、RGB16和 RGB24)的概念相关的技术文档? 我不确定我们的要求是否符合此分层设置。

我们需要叠加来自5个图层的显示数据、形成一个显示图像帧。

2.我认为您的 FPGA 是控制 LCD。 如果连接到 AM437x DSS、为什么仍然需要连接到 GPMC?

"我不知道你在说什么。" 您是否想要传达这样一种说法:由于 AM437x 通过 DSS 连接到 LCD、为什么需要 GPMC 连接到 FPGA?"

"我们的原始设计是 CPU+FPGA 系统、由 CPU 处理显示数据的呈现、然后将这些数据传输到 FPGA 进行覆盖设计(5层)并驱动 LCD 屏幕。 由于 GPMC 的当前使用无法满足显示数据的带宽要求、因此我们需要 CPU 处理 LCD 显示的渲染、分层和驱动。 但是、我们的系统仍有其他需要 FPGA 处理的功能、FPGA 仍需要将其他数据传输到 CPU。 因此、我们仍然需要保留 GPMC 接口。"

但 AM437x 的 DSS 功能和 GPMC 功能不能同时使用。

您好、Sheng:

是否有关于一个图形层(RGB 或 CLUT)和两个视频层(YUV 4:2:2、RGB16和 RGB24)概念的任何技术文档?

您是否已查看器件 TRM 第13.3.3.4节"重叠支持"?

[报价 userid="262629" url="~/support/processors-group/processors/f/processors-forum/1436435/am4372-how-to-implement-dma-transmission-between-am4372bzdna60-and-fpga/5527861 #5527861"]但是、我们的系统还有其他需要 FPGA 处理的功能、并且 FPGA 仍需要将其他数据传输给 CPU。 因此、我们仍需要保留 GPMC 接口。"好的、感谢您的澄清。

但无法同时使用 AM437x 的 DSS 函数和 GPMC 函数。

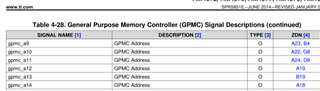

我认为、如果在 GPMC 上只使用最多12条地址线(焊球 A19将在 DSS 和 GPMC 中使用)、则可以在同一设计中同时使用 DSS 和 GPMC。

您好、 Bin Liu

"我已阅读器件 TRM 的第13.3.3.4节"叠加支持"。 不过,我还有几个问题。"

1、"图形层和视频层的组成有何区别? 为什么是一个图形层和两个视频层、而不是三个图形层或三个视频层?"

2、"覆盖管理器可配置为两种不同的模式:

•Alpha 模式(仅与带有源颜色键的图形层一起使用)

•正常模式(不支持 ALPHA)"

"这两种模式的区别在于,在一种模式中,图形层始终保持在视频层的上方,而在另一种模式中,图形层始终保持在视频层的下方。 在开发过程中如何选择这两种模式? "显示效果有何差异?"

您好、Sheng:

1、"图形层与视频层的构成有何区别? 为什么它是一个图形层和两个视频层而不是三个图形层或三个视频层?"

从应用角度来看、它们只是具有不同格式支持的流水线-图形层支持 RBG 或 CLUT、而视频层支持 YUV 和 RGB。

开发过程中如何选择这两种模式?"

该位应由 DSS 寄存器控制。 (我不再支持 DSS、上次我在 DSS 上工作是10多年前。)

显示效果有何区别?

TRM"重叠支持"一节对所有这些进行了介绍。

下面是正常模式的用例示例、希望这些示例有助于您了解:

当在4:3显示器上以16:9的比例播放电影的视频播放器实现时、显示器的顶部和底部将为空、视频播放器将填充纯色(通常为黑色)、这将在最后面的图形层上呈现。 然后,电影本身将在视频1层上呈现,该层占据了显示器的大部分,而闭合的字幕将呈现在影片顶部的视频2层上,该层通常靠近显示器底部。

您好、Sheng:

BTY、您是否考虑使用 AM62x 器件而不是 AM437x? AM62x 几年前刚刚发布、比 AM437x 具有更多的功能。 您可以查看 AM62x 器件数据表以了解它是否更适合您的项目。