工具与软件:

尊敬的 TI 工程师:

我们有一个使用 C6657 DSP 芯片的定制开发版本、我们使用的引导模式是 SRIO Boot。

我们的硬件架构采用 FPGA+DSP 设计。 FPGA 通过 SRIO 将映像写入 DSP、并在 DSP 上运行。 我们已成功测试此技术路线。 DDR 已通过 TI 提供的手册成功测试

现在我们要放置。 DDR 上的文本段、因此我们需要在引导阶段初始化 DDR。 通过阅读 SPRUG5C 用户手册、我们发现 TI 在引导表中提供了引导配置表来初始化 DDR。

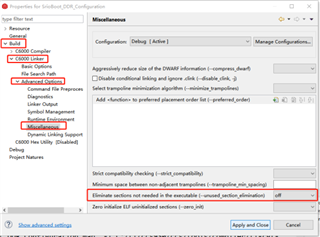

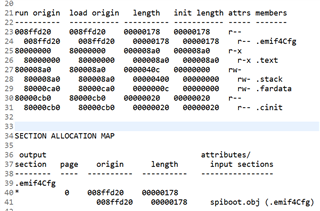

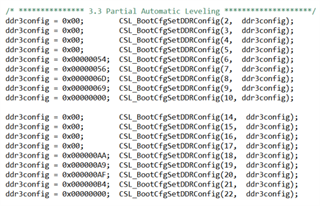

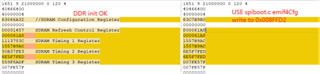

我们创建了一个项目来从 spidoot 移植代码。 C 写入我们的测试项目、并使用 SRIO 将 emif4Cfg 的内容写入0x008ffd20。 但是、测试后、DDR 未成功初始化。

因此、我有以下问题:

可以在 SRIO 引导表中添加 DDR 配置表、在 SRIO 引导期间初始化 DDR、然后写入。 文本段至 DDR。

2.如果问题的技术解决方案可行、是否只需要在 SRIO 引导中使用 DDR 配置表的初始化过程中将 emif4Cfg 的内容写入0x008ffd20? 我是否需要写入某些寄存器来触发 DDR 初始化?