工具与软件:

尊敬的专家:

我的主板上有16GB 的内存、每个 DDRSS 都连接到4GB 的内存。 假设我想为0x80000000至0xFFFFFFFF 区域启用 ECC、则配置的四个 DDRSS 寄存器如下:

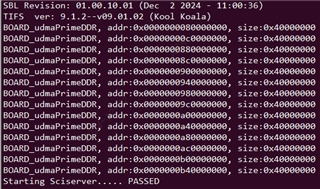

然后、我通过 SBL 中的 UDMA 将0x80000000写入已知模式的0xFFFFFFFF 部分。

但是、在启动期间仍会检测到 ECC 错误:

我的寄存器配置是否错误?

我们的 SDK 版本是09_01_00_06

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的专家:

我的主板上有16GB 的内存、每个 DDRSS 都连接到4GB 的内存。 假设我想为0x80000000至0xFFFFFFFF 区域启用 ECC、则配置的四个 DDRSS 寄存器如下:

然后、我通过 SBL 中的 UDMA 将0x80000000写入已知模式的0xFFFFFFFF 部分。

但是、在启动期间仍会检测到 ECC 错误:

我的寄存器配置是否错误?

我们的 SDK 版本是09_01_00_06

您好、Tao、

您能否确保为整个 DDR 启用它是否正常工作?

不支持开箱即用、即可启用部分 ECC。 此外、启用部分 ECC 的原因是什么。 取决于硬件设计

即使部分 ECC 启用也会占用整个 DDR 的1/8 (对于 ECC)。

-基尔西

1.我删除了 DTS 中最后2GB 内存:

内存@8000000{

device_type ="存储器";

/*(16-2)=14G RAM */

REG =<0x00 0x80000000 0x00 0x80000000>、

<0x08 0x80000000 0x03 0x00000000>;

};

2.启用部分 ECC:的原因

我们希望在执行高温和低温测试时保护内存低2GB。

我想知道如果我对较低的2GB 执行 ECC 保护、那么上述寄存器级配置是否正确。

我修改了 SBL 代码以支持对前14GB DDR 存储器的 ECC 保护、寄存器配置如下所示:

同时我删除了 DTS 中最后2GB 内存:

内存@8000000{

device_type ="存储器";

/*(16-2)=14G RAM */

REG =<0x00 0x80000000 0x00 0x80000000>、

<0x08 0x80000000 0x03 0x00000000>;

};

当 SBL 启动且 ECC 配置完成后、第一个14GB 存储器通过 UDMA 写入该模式:

系统正在运行、没有出现 ECC 错误。