主题中讨论的其他器件: SysConfig

工具与软件:

嗨、团队:

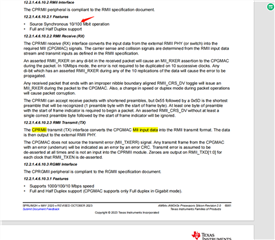

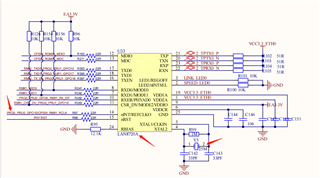

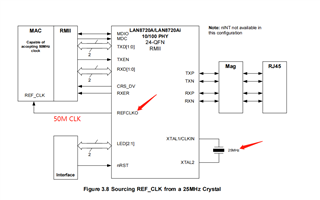

我在开发 RMII 接口时遇到问题:无法在100M 模式下运行 RMII。

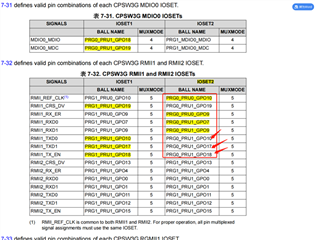

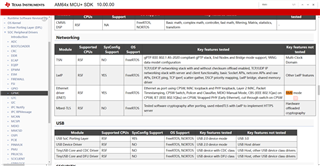

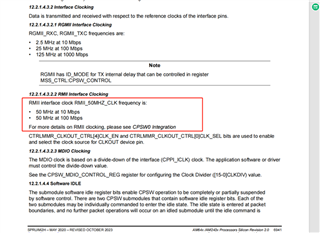

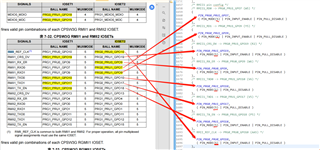

1) 1) 搜索找不到 RMII_EN、仅 GMII-IN 和 XGMII-EN (AM6442仅支持 RMII RGMII)、这些不在 AM6442 CPSW 的接口支持范围内。

如何确保 RMII 在100M 时工作?

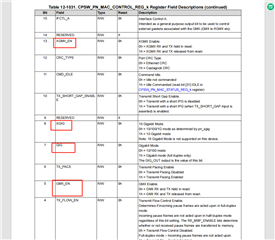

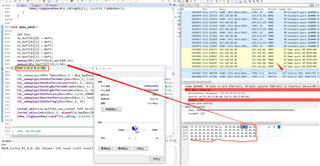

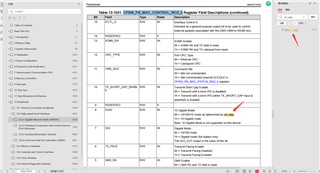

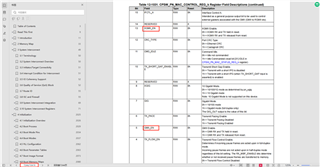

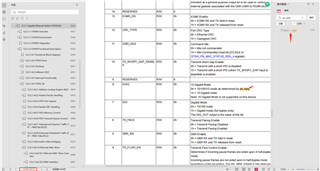

2) CPSW-PN_MAC-Conc-REG_k 寄存器位[8] XGIG 表示 MAC 传输速度取决于 pn-xig;TRM 无法检索 pn_xig 的相关指令? 如何使 RMII 在100模式下工作? (目前、10M 工作正常、但找不到100M 的设置方法)

3)

我猜是因为这个芯片不支持 RMII 100Mbps 模式。 我迫切希望你能提供一个简单的例子项目全双工100M 速率在 RMII 接口模式,反驳我的观点。

关于 CTL_EN 的说明、我搜索了整个 TRM、找不到寄存器的相应 CTL_EN。 我在 AM6442的开发过程中多次遇到类似的问题、因此我不再对 TRM 有很高的信任。 这也是我怀疑该芯片不支持 RMII 100Mbps 速度的原因之一。

我真的希望你的员工能够用事实来反驳我的观点;与其反复要求我提供日志、这个 CPSW 模块的 RMII 界面的开发对我来说是令人沮丧的(信息很少、上次我问问题时、他们总是简单地要求我提供日志。 我真的希望您可以编写自己的测试演示、我认为您也会遇到与我相同的困境)。

谢谢、此致、

Jiahui