工具与软件:

我们的客户在其定制电路板上对 LPDDR4执行合规性测试、发现写入访问存在问题。 DQS 和 DQ 之间几乎没有偏差、DQS 和 DQ 似乎同相。 另一方面、读取访问没有问题。

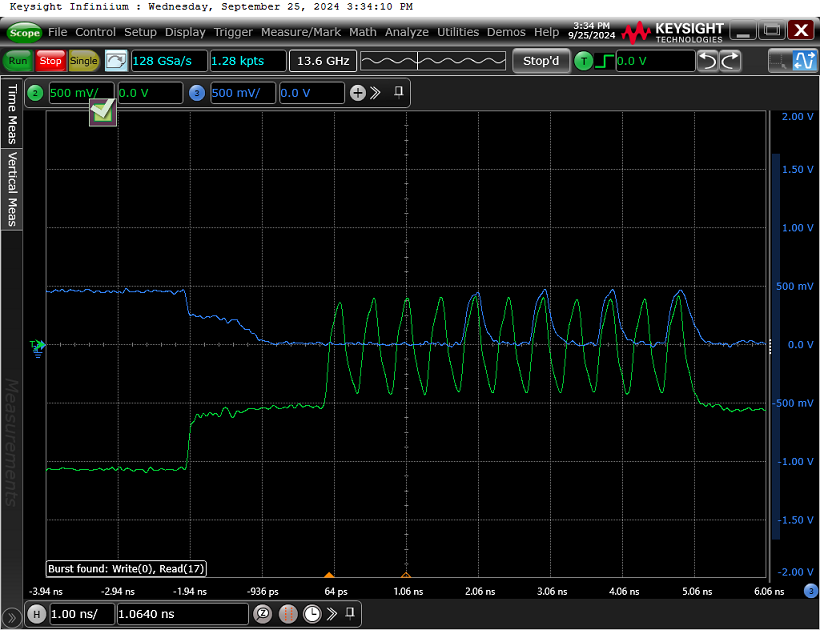

使用写入访问时的 DQS 至 DQ 偏差:

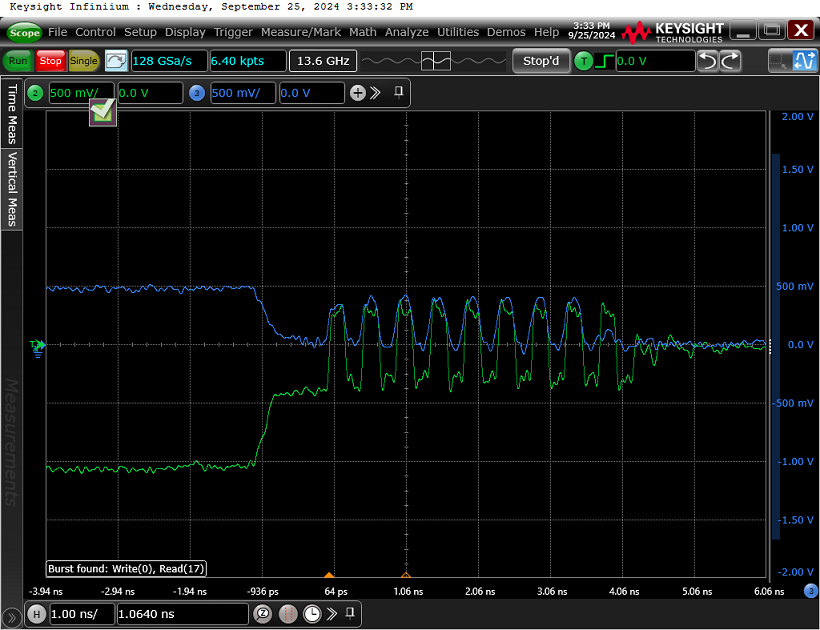

使用读取访问时的 DQS 至 DQ 偏差:

原图中的后仿真没有问题、因此硬件设计应该没有问题。

我们的客户担心写 DQS2DQ 培训无法正常工作。

是否可以手动调整 DQS 和 DQ 之间的相位? 如果是、如何实现?

从 DDRSS 寄存器配置工具 v0.11.0导出的 syscfg 文件随附:e2e.ti.com/.../CUSTUM_2D00_AM69_5F00_LPDDR4.syscfg.txt

此致、

大辅