工具与软件:

尊敬的 TI:

请帮助我检查我的配置是否正确。

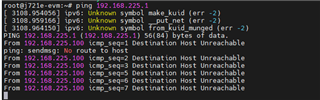

使用 TDA4的 CPSW9G、连接到 Phy 芯片、成功建立链路、但我们无法对其他器件执行 ping 操作

SDK-10.00

serdes0-lane1:rtl9010 (sgmii2)

配置

1.uboot:

2.linux dts k3-j721e-common-proc-board.dts

&SerDes_ln_ctrl{

空闲状态= 、 、

、 、

、 、

、 、

、 、

、 ;

};

&SerDes_wiz0 {

状态="正常";

};

服务器0 (&S){

状态="正常";

分配的时钟数=<&serdes0 cdns_Sierra PLL_CMLLC>、<&serdes0 cdns_Sierra PLL_CMNLC1>;

Assigned-clock-parents =<&wiz0_pll1_refclk>、<&wiz0_pll1_refclk>;

#address-cells =<1>;

#size-cells =<0>;

serdes0_SGMII_link:phy@0{

REG =<0>;

cdns, num-lannes =<2>;

#phy-cells =<0>;

cdn、phy-type = ;

重置=<&SerDes_wiz0 1>、<&SerDes_wiz0 2>;

};

};

cpsw0{

状态="正常";

};

cpsw0_port2 {

状态="正常";

phy-handle =<&cpsw9g_phy1>;

PHY 模式="SGMII";

MAC-ADDRESS =[00 00 00 00];

phys =<&cpsw0_phy_gmii_sel 2>、<&serdes0_SGMII_link>;

PHY-names ="portmode"、"SerDes-phy";

};

cpsw9g_mdio{

状态="正常";

pinctrl-names ="默认值";

pinctrl-0 =<&mdio0_pins_default>;

RESET-post-delay-us =<120000>;

#address-cells =<1>;

#size-cells =<0>;

cpsw9g_py1:ethernet-phy@1{

reg =<1>;

compatible ="ethernet-phy-id001c.cb30"、"ethernet-phy-IEEE802.3-c22";

固定链接{

速度=<1000>;

全双工;

};

};

};

删除 J7-MAIN-r5f0_0-FW

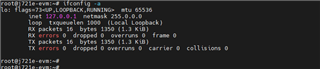

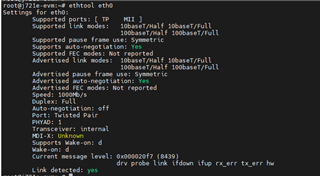

4. ethtool eth0

5.引导日志