主题中讨论的其他器件: CDCE6214

工具与软件:

大家好

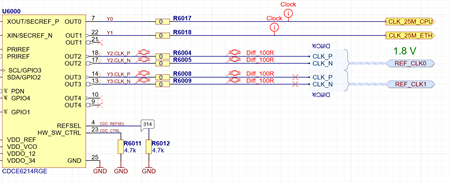

我们遇到了 AM6442 CPU 的技术问题。 我们使用外部时钟发生器 (CDCE6214) 作为 PCIe 的100Mhz 时钟源。 现在我们假设在 CPU 侧有一个内部下拉电阻器负责解决我们的问题。 时钟提供器在 LP-HCSL 模式下运行、接线如下所示:

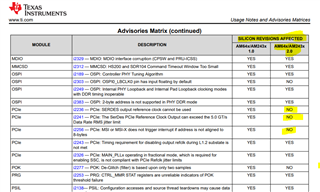

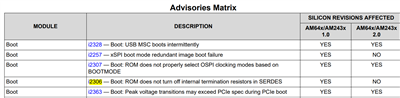

根据勘误表 https://www.ti.com/lit/er/sprz457h/sprz457h.pdf、 不能使用 SERDES 输出参考时钟(i2236)。

另一个原因也是 i2241: PCIe:串行器/解串器 PCIe 参考时钟输出可能会超过5.0 GT 每秒数据速率 RMS 抖动限制

现在、根据我们的测量和想法、我们假设有一个内部下拉电阻器负责解决我们的问题。

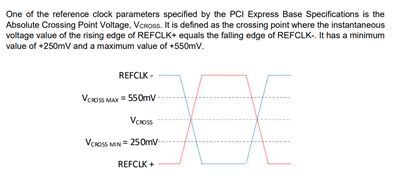

电压电平太低、根据 PCIe 标准(电压交叉)不够高。

PCIe 时钟信号的交叉电压:

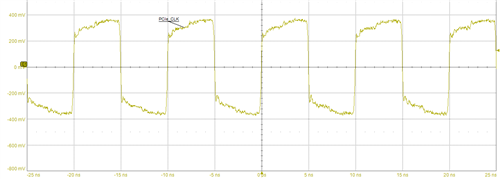

在这里、我们测量的信号、我们看到最终得到200mV 的交叉电压:

.

是否有任何内部电阻器会影响 CPU 端口 W17 SERDES0_REFCLK0P 和 W18 SERDES0_REFCLK0P ?

您能否确认存在内部端接电阻、如果可以将其关闭、我们必须执行什么寄存器写入来将其关闭?