主题中讨论的其他器件: SysConfig

工具与软件:

您好!

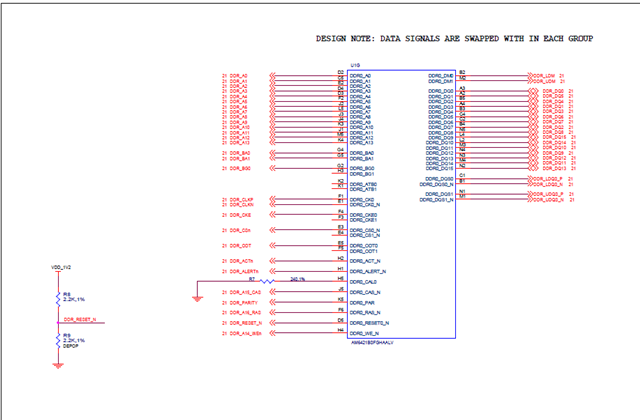

我们有一个采用 SOC AM6421 1GB K4A8G165WB-BCRC DDR 的定制电路板。

我们使用的是 mcu_plus_sdk_am64x_09_02_00_50 SDK。

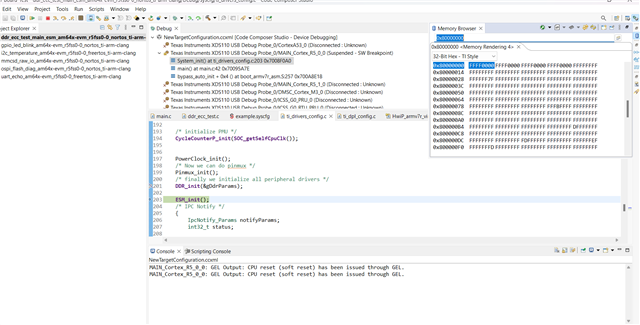

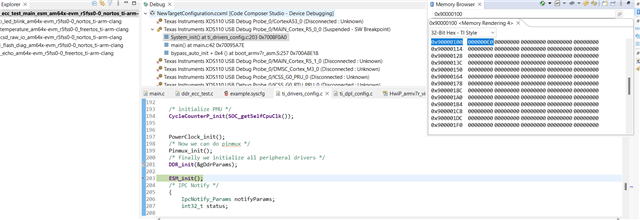

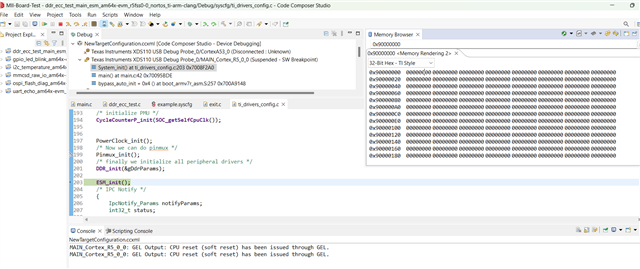

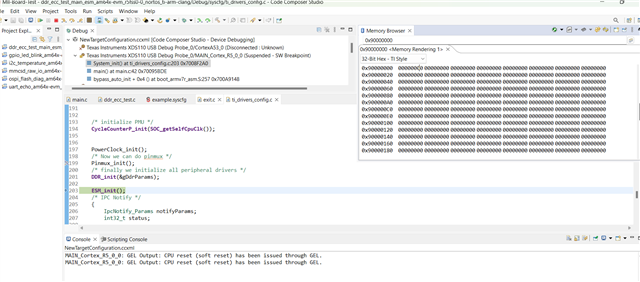

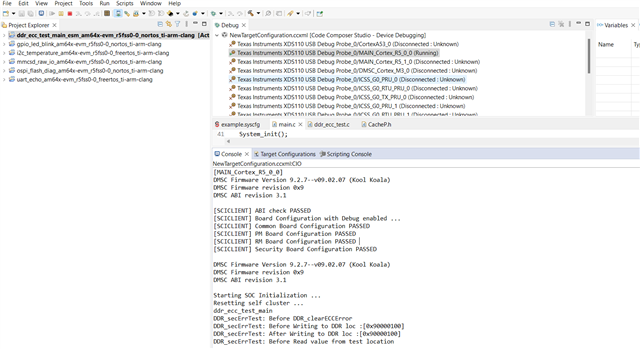

我们将使用 SDK 示例中的示例 DDR_ECC_TEST_MCU_ESM 测试硬件。

我们正面临这一问题

代码如下所示

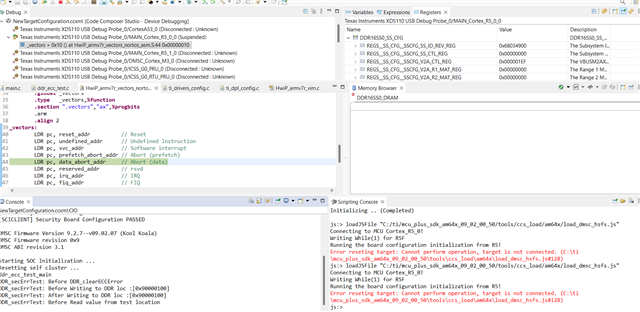

当运行时、执行在线上停止

testVal = g Test_Addr [0];

背面接地:

同样的示例适用于我们之前的板、即10层板、使用了相同的 DDR 和 SOC。

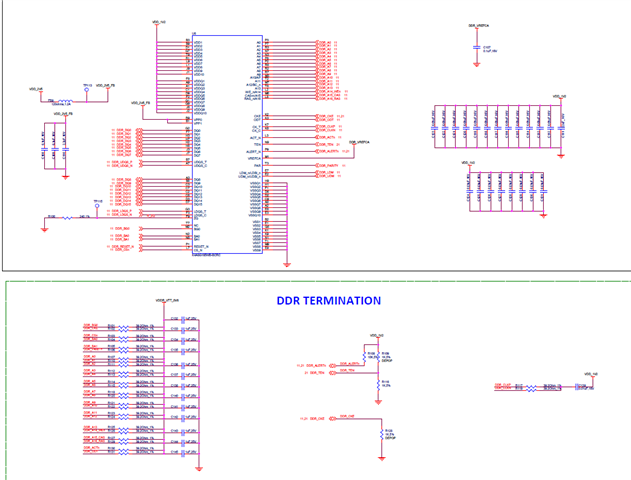

我们的新电路板具有12层、ICCSS 接口更改为 MII。

我们已检查12层空 PCB 布线长度和跟踪阻抗并发现它们在指定范围内。

可以帮助我们解决这个问题。

谢谢你。