工具与软件:

在"u-boot"中、'm 正在尝试检测 TDA4AL SoC 上的 Marvell 88q2112 PHY 器件

但未找到"以太网"。 如何解决此问题。

NAME=Marvell 88Q2112、uid=2820480、mask=268435440、phy_id=2820480

以太网@46000000port@1连接到 Marvell 88Q2112模式 RGMII-rxid

PHY_CONNECT:1044

initQ2112Ge

_applyQ2112设置

getAcegEnabled

@3. 未找到以太网。

=> MDIO 列表

MDIO@f00:

以太网@46000000port@1:

7 - Marvell 88Q2112 <->以太网@46000000port@1.

=> MII 读0-1 0-6

从 PHY addr=00 reg=00读取时出错

从 PHY addr=00 reg=01读取时出错

从 PHY addr=00 reg=02读取时出错

MDIO 读取1 1

1不是已知的以太网

从总线 MDIO@f00读取

地址1处的 PHY:

错误

=> MDIO 读取0x1 0x0900

0x1不是已知的以太网

从总线 MDIO@f00读取

地址1处的 PHY:

错误

别名{

Ethernet0 =&cpsw_port1;

};

+ mcu_eth0_pins_default:mcu-eth0-pins-default{

PINCTL-SINGLE、PINS =<

+ J721S2_WKUP_IOPAD (0x054、PIN_INPUT、7)/*(E28) WKUP_GPIO0_61 ETH_SOC_INT */

+ J721S2_WKUP_IOPAD (0x050、PIN_OUTPUT、7)/*(E27) WKUP_GPIO0_60 SOC_ETH_PHY_RESET */

>;

};

&Davinci_MDIO{

phy0:Ethernet-phy@0{

- reg =<0>;

+ reg =<7>; /*根据原理图*/

TI、Rx 内部延迟= ;

TI、FIFO 深度= ;

TI、最小输出阻抗;

+ compatible ="ethernet-phy-id002b.0980";

+ ti,dp83867-rxctrl-strap-quirk;

+ reset-assert-us =<100>;

+ reset-deassert-us =<280>;

+ RESET-GPIO =<&EXP1 60 GPIO_ACTIVE_HIGH>;

};

};

cpsw_port1{

+状态="正常";

PHY-MODE ="RGMII-rxid";

PHY-Handle =<&phy0>;

+ pinctrl-0 =<&MCU_eth0_pins_default>;

};

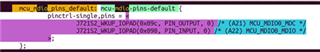

mcu_cpsw_pins_default:mcu-cpsw-pins-default{

PINCTL-SINGLE、PINS =<

J721S2_WKUP_IOPAD (0x094、PIN_INPUT、0)/*(B22) MCU_RGMII1_RD0 */

J721S2_WKUP_IOPAD (0x090、PIN_INPUT、0)/*(B21) MCU_RGMII1_RD1 */

J721S2_WKUP_IOPAD (0x08c、PIN_INPUT、0)/*(C22) MCU_RGMII1_RD2 */

J721S2_WKUP_IOPAD (0x088、PIN_INPUT、0)/*(D23) MCU_RGMII1_RD3 */

J721S2_WKUP_IOPAD (0x084、PIN_INPUT、0)/*(D22) MCU_RGMII1_RXC */

J721S2_WKUP_IOPAD (0x06c、PIN_INPUT、0)/*(E23) MCU_RGMII1_RX_CTL */

J721S2_WKUP_IOPAD (0x07c、PIN_OUTPUT、0)/*(F23) MCU_RGMII1_TD0 */

J721S2_WKUP_IOPAD (0x078、PIN_OUTPUT、0)/*(G22) MCU_RGMII1_TD1 */

J721S2_WKUP_IOPAD (0x074、PIN_OUTPUT、0)/*(E21) MCU_RGMII1_TD2 */

J721S2_WKUP_IOPAD (0x070、PIN_OUTPUT、0)/*(E22) MCU_RGMII1_TD3 */

J721S2_WKUP_IOPAD (0x080、PIN_OUTPUT、0)/*(F21) MCU_RGMII1_TXC */

J721S2_WKUP_IOPAD (0x068、PIN_OUTPUT、0)/*(F22) MCU_RGMII1_TX_CTL */

>;

};