工具与软件:

SDK:0902 0806

电路板:tda4vm_evm

尊敬的 TI 专家:

sdk_builder/

编译 vision_app 时、我需要先编译:

make sdk -j2

然后、我编译 vision_app mcu1_0:

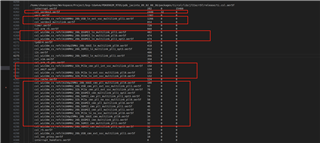

make vision_apps -j 1 PROFILE=release BUILD_CPU_MCU1_0=yes BUILD_CPU_MPU1=no BUILD_CPU_MCU2_0=no BUILD_CPU_MCU2_1=no BUILD_CPU_MCU3_0=no BUILD_CPU_MCU3_1=no BUILD_CPU_C6x_1=no BUILD_CPU_C6x_2=no BUILD_CPU_C7x_1=no

但我看到在实际编译的.out.map 文件中也编译了许多无用的库文件。 这将大大增加我的代码:的数量

这是因为我首先要编译静态库、然后编译应用、再在链接时链接中的所有静态库。 我应该在哪里修改哪些链接参数来避免此问题?

此致

伊森