工具与软件:

尊敬的团队:

我们希望在 AM68A 上进行离散时间同步。 我们有外部10MHz 主时钟和 PPS 需要连接到 AM68A CPTS、我们该怎么做?

在本例中、我们有 两个来自 AM64主10MHz clk 信号和 PPS 信号的信号。

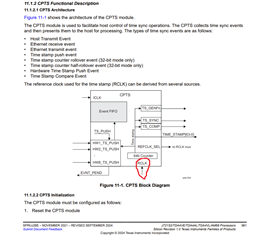

理念是将 PPS 信号连接到 CPTS0_HW2TSPUSH (AD28)、将10MHz clk 连接到 CPTS0_REF_CLK (AB26)

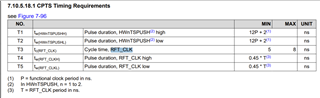

但我们注意到、根据 DS、CPTS0_REF_CLK 仅接受从125MHz 到200MHz 的时钟范围。 是否正确、或者我们是否也可以将10MHz clk 用于该输入?

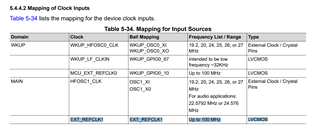

另一个想法是使用 EXT_REFCLK1 (可接收 高达100MHz clk 的数据)、但我们看到、这不能 路由到 CPTS0 RCLK、是正确的吗?

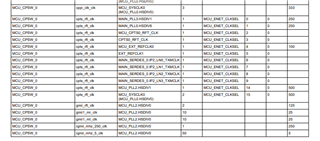

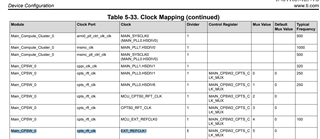

-> 表5-32. PLL 控制的模块未在表中显示 EXT_REFCLK1?

-> 表5-33。 时钟映射显示 EXT_REFCLK1可以连接到 CPT_RFT_clk?

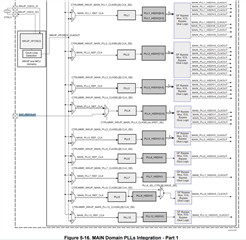

-> EXT_REFCLK1只能按照下面的图片路由到 PLL4 ?

此致、

D.