工具与软件:

SDK:0,902,0806

电路板:TDA4_EVM

您好、 TI 专家:

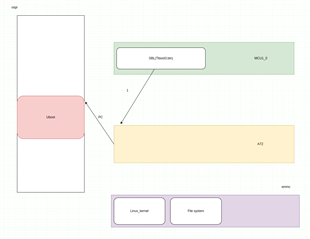

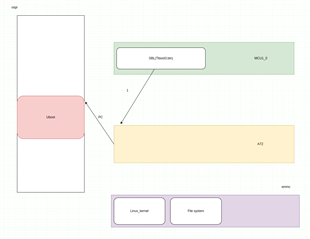

现在我们有了以下启动过程设计。( 让 SBL 将 A72的 PC 指针设置为直接指向存储在 ospi 中的 uboot):

我们从 ospi 开始。 同时、我们需要 uboot 在 ospi (XIP)上运行、而不是在 DDR 上运行。 我们需要如何设置和编译 uboot? 如何编写 SBL 代码?

谢谢!

伊森

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

SDK:0,902,0806

电路板:TDA4_EVM

您好、 TI 专家:

现在我们有了以下启动过程设计。( 让 SBL 将 A72的 PC 指针设置为直接指向存储在 ospi 中的 uboot):

我们从 ospi 开始。 同时、我们需要 uboot 在 ospi (XIP)上运行、而不是在 DDR 上运行。 我们需要如何设置和编译 uboot? 如何编写 SBL 代码?

谢谢!

伊森

有什么建议吗? [报价]您好、伊森

我选中这一项、希望 BU 给出建议

此致

Semon

您好、Semon

非常感谢您的答复。

我必须再次询问、我是否仍需要 ATF_OPTEE? 如有必要、如何编译它?

因为我使用这种启动方法:μ s

1.如何编译合并的 dev.appimage? (atf+opte+a72 spl)并将其刷写到 ospi 上的哪个位置?

2.启用 CONFIG_SPL_XIP_SUPPORT 后、是否仍需要修改 uboot 链接文件? 编译后的 uboot.img 应该写入 ospi 的哪个地址?

3. SBL 需要修改什么代码才能启动 combined_dev.appiamge? 我在 sbl_main.c 中没有看到相关代码

此致、

伊森

你好、伊森

您可以在 j721e_spi.h 中定义此宏、如下所示:

--------------------------------------------------------

/*引导模式 B = 0 */

#include

#define BOOT_DEVICE_HYPERFLASH 0x00

#define BOOT_DEVICE_OSPI 0x01

#define BOOT_DEVICE_QSPI 0x02

#define BOOT_DEVICE_SPI 0x03

#define BOOT_DEVICE_ETHERNET 0x04

#define BOOT_DEVICE_I2C 0x06

#define BOOT_DEVICE_UART 0x07

#define BOOT_DEVICE_NOR BOOT_DEVICE_HYPERFLASH

#define BOOT_DEVICE_XIP BOOT_DEVICE_OSPI

--------------------------------------------------------

您好、Semon

感谢您的回答。 现在、我已经成功编译了以下固件、但固件似乎没有什么不同:

Q1:

我仍然需要 ATF_OPTEE? 如有必要、如何编译它? 这是 我的启动:

问题2:

如何编译合并的 dev.appimage? (atf+opte+a72 spl)并将其刷写到 ospi 上的哪个位置?

Q3:

我需要在 SBL_main 中进行哪些修改? 有演示吗?

此致、

伊森

你好、伊森

好的、我将让研发部门来调查这个问题

此致

Semon

您好、Semon

我有一个案例、其中 SBL 启动 mcu1_0。 Mcu1_0也在 ospi (XIP)上运行、并已成功启动。 下面是启动图:

引导流程:

Tibooot3.bin 在 ocmc 中运行。

2、SBL 在 ocmc 中复制"虚拟应用程序1"、并运行"虚拟应用程序1"

3、"虚拟应用1"跳转至0x501c0000m、其中 存储 mcu1_0应用。

所以我认为对于 A72内核、如果我想 uboot 在 ospi (XIP)中运行、也可以执行此:

(ATF+OPTEE+SPL)= combined_dev.appimage、其中 SBL 可以引导映像格式。

1、A72 SRAM (或 ram)中的 SBL 复制 combined_dev.appimage

2、combined_dev.appimage 运行并为 linux_kernel 否 初始化 DDR(以进行 uboot)和 A72系统初始化。

3、combined_dev.appimage 跳转到 存储在 ospi 中的 uboot.bin 的起始地址。

4、uboot 正在运行并从 eMMC 引导 Linux_kernel。

此致、

伊森

你好、伊森

BU 确认、TI 从未在 XIP 模式下验证 u-boot、如果需要、应提供一个新功能。

您能解释一下为什么您需要 u-boot 在 XIP 中运行、事实上 SPL 已经在 SRAM 中运行、并将 u-boot 加载到 DDR 以运行吗

有什么特别的要求吗?

此致

Semon

您好、Semon

感谢您的答复。

我想让 uboot XIP 运行的原因很长。

我们希望 mcu1_0在上电后的100ms ([50,100) ms)内发送 CAN 消息的第一个帧、但我们的 mcu1_0的代码超过1M、因此 can_early_response 演示不适合我们的项目。 (__LW_AT__因为 can_early_responce 演示都在 ocmc 中运行,但 ocmc 仅为1M ,且 ocmc 需要与 mcu1_0 app、sbl 和 ROM 代码共享。)

在 SBL 中、该 TI 专家已确认初始化 DDR 的时间超过30ms。

因此、为了无需初始化 DDR 和减少 SBL copy mcu1_0的代码运行地址、我根据 SDK 中的演示设计了 mcu1_0的 XIP 运行、操作成功。

在默认 SDK 中、uboot 和 Linux_kernel 在 DDR 中运行、因此在 uboot 和 Linux_kernel 启动之前、必须初始化 DDR。 不在 SBL 中初始化 DDR 时、会发生此冲突。

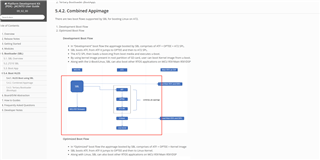

后来,我在文档中找到了第二种启动 HLOS 的方法,如下图中的红框所示:

这与 can_boot_app 演示类似、但我们不想添加代码来在 mcu1_0中启动其他内核、而是将所有启动过程置于 SBL 中、因此我们也不选择此选项。

最后、只有一种方法。 我希望 uboot 直接在 ospi (XIP)中运行并延迟 DDR 的初始化(在 SPL 或 uboot 中)、但需要在运行 Linux_kernel 之前初始化 DDR。

因此、如果我无法在 SBL 中初始化 DDR、让 uboot 在 ospi (XIP)上运行、并在 uboot 中初始化 DDR、然后再启动 Linux_kernel 运行、则上述所有问题均可解决。

或者 uboot 可能无法在 ospi (无需 XIP)下运行、但 combined_dev.appimage 可以在启动 uboot 之前初始化 DDR、然后将 uboot 从启动地址(ospi)复制到运行地址(DDR)。 通过这种方式,上述所有问题也将得到解决。

或者 TI 专家还能提供其他任何解决方案吗?

此致

伊森