工具与软件:

亲爱的支持者、

我尝试使用 L2SRAM 在 MCU SDK 10上运行 C7x hello world FreeRTOS 示例。 默认链接器会将所有段路由到 DDR、我需要堆栈和堆路由到 L2SRAM。 但我只能将.sysmem 指向 SRAM。 只要我将.stack 指向 SRAM、调试器就无法跳转到主函数。 您能帮助我更改链接器以便让 Hello world FreeRTOS 项目在 SRAM 上运行吗?

非常感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

亲爱的支持者、

我尝试使用 L2SRAM 在 MCU SDK 10上运行 C7x hello world FreeRTOS 示例。 默认链接器会将所有段路由到 DDR、我需要堆栈和堆路由到 L2SRAM。 但我只能将.sysmem 指向 SRAM。 只要我将.stack 指向 SRAM、调试器就无法跳转到主函数。 您能帮助我更改链接器以便让 Hello world FreeRTOS 项目在 SRAM 上运行吗?

非常感谢!

尊敬的 Jack:

感谢您的耐心。

您可以尝试使用以下 linker.cmd 文件吗?

--ram_model

-heap 0x20000

-stack 0x20000

--args 0x1000

--diag_suppress=10068 /* to suppress no matching section error */

--cinit_compression=off

-e _c_int00_secure

#define DDR0_ALLOCATED_START 0x80000000

#define C7X_ALLOCATED_START DDR0_ALLOCATED_START + 0x19800000

#define C7X_RESOURCE_TABLE_BASE (C7X_ALLOCATED_START + 0x00100000)

#define C7X_BOOT_BASE (C7X_ALLOCATED_START + 0x00200000)

#define C7X_VECTOR_BASE (C7X_ALLOCATED_START + 0x00400000)

#define C7X_DDR_SPACE_BASE (C7X_ALLOCATED_START + 0x00410000)

MEMORY

{

L2SRAM (RWX): org = 0x7E000000, len = 0x00100000

DDR0_RESERVED: org = 0x80000000, len = 0x19800000 /* Reserved for A53 OS */

C7X_IPC_D: org = C7X_ALLOCATED_START, len = 0x00100000 /* 1MB DDR */

C7X_BOOT_D: org = C7X_BOOT_BASE, len = 0x400 /* 1024B DDR */

C7X_VECS_D: org = C7X_VECTOR_BASE, len = 0x4000 /* 16KB DDR */

C7X_CIO_MEM: org = C7X_DDR_SPACE_BASE, len = 0x1000 /* 4KB DDR */

C7X_DDR_SPACE: org = C7X_DDR_SPACE_BASE+0x1000, len = 0x01BF0000-0x1000 /* 27.9MB - 4KB DDR */

}

SECTIONS

{

boot:

{

boot.*<boot.oe71>(.text)

} load > C7X_BOOT_D ALIGN(0x200000)

.vecs > C7X_VECS_D ALIGN(0x400000)

.secure_vecs > C7X_DDR_SPACE ALIGN(0x200000)

.text:_c_int00_secure > C7X_DDR_SPACE ALIGN(0x200000)

.text > C7X_DDR_SPACE ALIGN(0x200000)

.bss > C7X_DDR_SPACE /* Zero-initialized data */

RUN_START(__BSS_START)

RUN_END(__BSS_END)

.data > C7X_DDR_SPACE /* Initialized data */

.cinit > C7X_DDR_SPACE /* could be part of const */

.init_array > C7X_DDR_SPACE /* C++ initializations */

.stack > L2SRAM

.args > C7X_DDR_SPACE

.cio > C7X_CIO_MEM

.const > C7X_DDR_SPACE

.switch > C7X_DDR_SPACE /* For exception handling. */

.sysmem > L2SRAM /* heap */

GROUP: > C7X_DDR_SPACE

{

.data.Mmu_tableArray : type=NOINIT

.data.Mmu_tableArraySlot : type=NOINIT

.data.Mmu_level1Table : type=NOINIT

.data.gMmu_tableArray_NS : type=NOINIT

.data.Mmu_tableArraySlot_NS : type=NOINIT

.data.Mmu_level1Table_NS : type=NOINIT

}

.benchmark_buffer: > C7X_DDR_SPACE ALIGN (32)

}

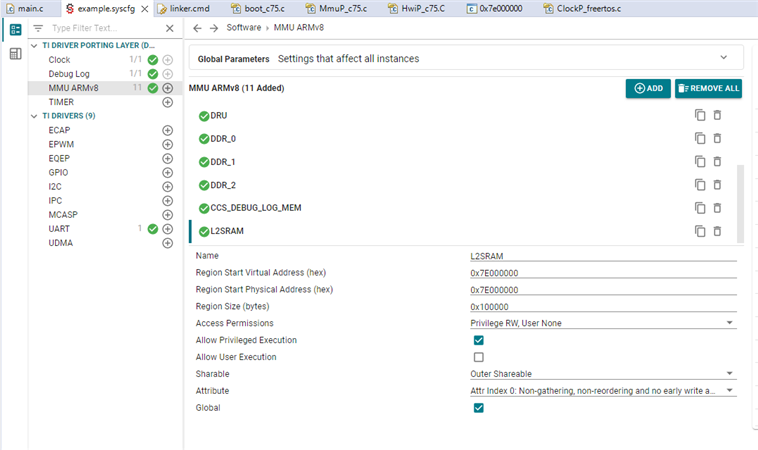

同时为 L2SRAM 存储器区域添加 MPU 区域条目。 请参阅下面的屏幕截图。

请告知我们上述解决方案是否有效。

此致、

Tushar

尊敬的 Tushar Thakur:

感谢您的支持、我可以使用链接器和 MMU 设置运行。 但是、当我想确认它是否真正在 L2SRAM 上运行时、有一个奇怪的情况。 我编写了一个小测试、以查看指针地址是否实际位于 SRAM 上、局部变量是否位于堆栈(SRAM)上。 但当我禁用优化时、我看到指针地址位于 DDR 上。 当我将优化级别更改为0或1时、我在 SRAM 上看到它。

为什么优化关闭使 DDR 上的指针即使在 L2上设置链接器.sysmem 也是如此?

选择关闭

选项1

感谢您的支持、

插孔