工具与软件:

尊敬的支持团队:

我们的客户报告了以下故障。

[故障概述]

应用程序: 监视监视器

情况:

通过有线 LAN 将监护仪连接到主监护仪,并在主监护仪上进行集中监测,以获取波形。

在这种情况下、主监控器上的波形在0.5s 至10s 之间中断是一个问题。

-以太网的传输波形没有问题,传输 从主机端从未停止。

-当传输波形中断时, 监控监视器内的 PHY (LAN8710AI)被轻轻复位。

-评估结果显示,当传输波形中断时,

监控监视器内的 PHY (LAN8710AI)已软复位。

-当我们检查此重置的原因时,我们发现它是由于丢失或无法识别的数据包

丢弃这些数据。

-我们检查了 Ether 和 RMII 的波形,没有发现任何明显的缺失波形

RMII 中的隐性状态。

(由于观察到了波形、因此无法确认波形质量

而设备嵌入到设备中。)

-这种模型已经批量生产了大约10年,直到现在都没有问题,

但是、2023年10个器件中有6个器件制造、20个器件中有13个器件制造

在最近一段时间里 、最初出现的缺陷是电路板有缺陷。

-我们目前正在调查问题的原因,但根据目前的调查结果,

我们认为 AM1808 EMAC 的 RMII 接收侧电路可能会出现某种故障。

详细信息如下所述。

我们的调查结果:

在此电路板上、阻尼电阻放置在 AM1808的 RMII_MHz_50_CLK (引脚 W18)附近。

当该阻尼电阻的常数为10Ω 时、就会出现问题、

但是、当它更改为0Ω 或22Ω 时、不会出现问题。

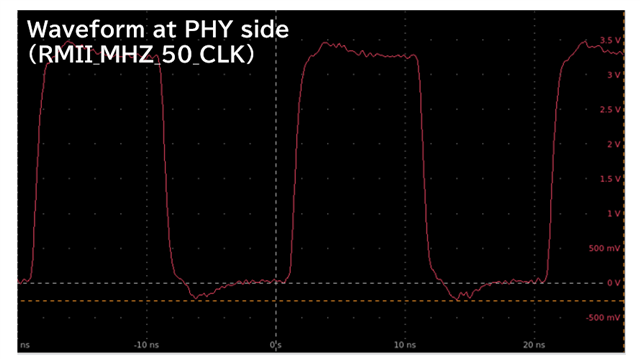

RMII_MHz_50_CLK 的波形:

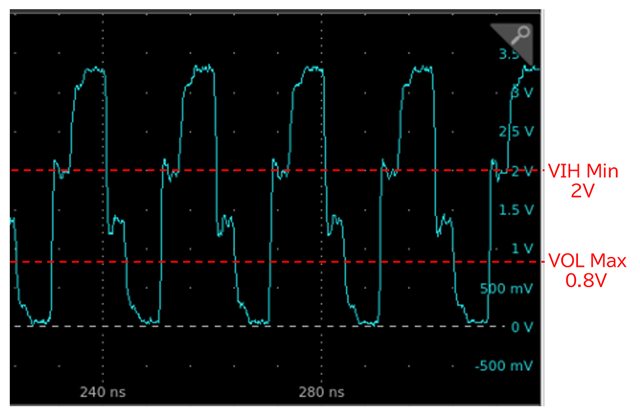

在发送器侧(AM1808 W18引脚附近)观察到波形、因此发生步进。

在接收端(LAN8710AI)观察到的波形(包括建立/保持时间)没有问题。

RMII_MHz_50_CLK 是输入/输出引脚。 阻抗将会降低

转换时间为5ns 或以上(0.25P 或以上)、是否可能出现这种情况

在中间电位下、一个流经输入缓冲器的流经电流导致问题吗?

如果您能指出任何其他关注点、我们将不胜感激。

此致、

Kanae