主题中讨论的其他器件:SK-AM62、 SK-AM62-LP、SK-AM62B-P1 、 SysConfig

工具与软件:

大家好、团队成员:

我的客户正在配置 DDR。 我看到有适用于 SK-AM62和 SK-AM62-LP 的参考设计、但没有适用于 SK-AM62B-P1 数字签名。

您能否为我的客户提供这些文件?

此致、

Mari Tsunoda.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

我的客户正在配置 DDR。 我看到有适用于 SK-AM62和 SK-AM62-LP 的参考设计、但没有适用于 SK-AM62B-P1 数字签名。

您能否为我的客户提供这些文件?

此致、

Mari Tsunoda.

尊敬的 Mari:

SK-AM62B-P1是带 PMIC 的 SK-AM62 EVM。 我可以看到两个 EVM 使用相同的 DDR4器件型号。 因此、您可以将 SK-AM62参考设计用于相同的 DDR 配置。

请参阅 SK-AM62用户指南 以了解详细信息。

此致、

Tushar

大家好、Mari、我收到了数据表。 所以主要的配置是拓扑结构:

数据总线宽度(每个器件)= 8

密度(每个器件)= 16

芯片选择/等级= 1

某些 IO 设置(驱动强度和端接)可能需要根据其电路板仿真(如所示)进行更改、但在其他方面应相同。 请确保他们遵循 DDR 布局指南应用手册 https://www.ti.com/lit/pdf/sprad06

此致、

James

尊敬的 Mari:

他们按照此处的建议进行了配置、但 Linux 无法看到4GB 的 DDR。 只能看到2GB。 [报价]请附加完整的控制台引导日志以显示2GB 问题。

您好、Bin、

我要求客户提供这些信息。

同时、您能告诉我配置4GB DDR 的典型过程吗? 我无法访问 AM62x Academy 链接来分配外设、因此如果您可以在 E2E 帖子中为我写下该文章、那会很好。

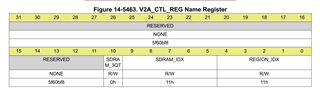

此外、他们已经从 0x0000000880000000在 devicetre 中配置了上部2GB、并且 U-Boot 正在识别该情况、但 k3-ddrss.c 中 k3_ddrss_DDR_reg_init ()中的 V2A_CTL_REG 寄存器似乎 不正确。 他们已经尝试修正此寄存器值、但效果不好。

此致、

Mari

尊敬的 Mari:

这是指向 Academy U-Boot 板端口页面的链接。 展示了如何将 U-Boot devicetre 从2GB 修改到512MB DDR。 对于4GB DDR、您需要在 devicetre 中添加第二个 DDR 存储器区域。 听起来这是客户所做的。

但是 k3-ddrss.c 中 k3_ddrss_ddrss_reg_init ()中的 v2a_CTL_REG 寄存器似乎 不正确。 他们已经尝试修复此寄存器值、但效果不佳。

另外、请提供详细信息或日志、以显示不好的方面。

您好、Bin、

他们尚未提供 U-boot 的日志、但他们读取的寄存器值如下所示。

V2A_CTL_REG (0x0F300020):

f1 01 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

另外、他们还发送了 dtsi 文件。

e2e.ti.com/.../k3_2D00_am62x_2D00_ddr_2D00_config.dtsi

似乎是针对 DDR4配置了.dtsi 文件、使 SDRAM_IDX=16、REGION_IDX=17、因此不应读取这些值。

什么地方可能会出错? 我将与客户通话、以便能够讨论可能的原因。

此致、

Mari

尊敬的 Mari:

我真的需要查看 U-Boot 日志、并了解客户使用的是哪个处理器 SDK 版本。

在 SDK9.2 (及更旧) U-Boot 中、如果定制电路板对 AM62x 使用除2GB 以外的不同 DDR 大小、则必须在 U-Boot 源代码中手动更改 V2A_CTL_REG。

但是、自 SDK10.0以来、U-Boot 代码已得到改进、以根据 DDR 配置数据调整 V2A_CTL_REG 值。

您好、Bin、

按照 SDK 版本、您是指 PSDK 版本正确吗? 我还在等待客户提供这些信息。

但是自 SDK10.0以来、U-Boot 代码经过改进、可根据 DDR 配置数据调整 V2A_CTL_REG 值。

客户是否成功将 DDR4设置为4GB? 我发现很多客户都遇到了问题、但可能主要是关于旧版 SDK ...

此致、

Mari Tsunoda.

客户是否成功设置了4GB DDR4? [报价]我从不注意这一点、但我相信我们确实有客户在 AM62x 器件上运行4GB DDR。

[报价 userid="499871" url="~/support/processors-group/processors/f/processors-forum/1430375/am625-ddr-config-for-sk-am62b-p1/5572023 #5572023"]为了检查、在他们从 DDR SysConfig 生成.dtsi 文件后、一般思路是将文件添加到 U-Boot 和内核 dts 文件夹中、是否正确? 然后他们重建并应该能够看到大2GB?

有。

您好、Bin、

这是来自 U-boot 的日志。 SDK 版本为10.00。

U-Boot SPL 2024.04-ti-gfda88f8bcea3 (Jul 26 2024 - 11:00:12 +0000) SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') video_reserve: Reserving 900000 bytes at ff700000 for video device 'dss@30200000' Video frame buffers from ff700000 to 100000000 Reserving 9216k for video at: ff700000 SPL initial stack usage: 1856 bytes tidss_drv dss@30200000: video port 2 clock enable error -22 Trying to boot from MMC2 Authentication passed Authentication passed U-Boot 2024.04-ti-gfda88f8bcea3 (Jul 26 2024 - 11:00:12 +0000) U-Boot code: 80800000 -> 808E9010 BSS: -> 808EEBD8 SoC: AM62X SR1.0 HS-FS Model: TOPCON AM625 EEMC 0101 EEPROM not available at 0x50, trying to read at 0x51 Reading on-board EEPROM at 0x51 failed -19 DRAM: Monitor len: 000EEBD8 Ram size: 80000000 Ram top: 100000000 Reserving 0k for video at: ffff0000 Reserving 954k for U-Boot at: fff01000 Reserving 32892k for malloc() at: fdee2000 Reserving 152 Bytes for Board Info at: fdee1f60 Reserving 480 Bytes for Global Data at: fdee1d80 Reserving 73728 Bytes for FDT at: fdecfd80 RAM Configuration: Bank #0: 80000000 Bank #1: 880000000 DRAM: 2 GiB (effective 4 GiB) New Stack Pointer is: fdeceff0 Copying bloblist from 0000000080d00000 to 00000000fdecf000, size 400 Relocation Offset is: 7f701000 Relocating to fff01000, new gd at fdee1d80, sp at fdeceff0 video_post_bind: gd->video_top 0 video_post_bind: addr fff39b08 video_post_bind: addr ffffffffff700000 video_post_bind: Claiming 900000 bytes at ffffffffff700000 for video device 'dss@30200000' Core: 79 devices, 31 uclasses, devicetree: separate MMC: mmc@fa10000: 0, mmc@fa00000: 1 Loading Environment from nowhere... OK video_post_probe : 545 video_post_probe : 577 gd->video_bottom = 0x0 "Synchronous Abort" handler, esr 0x96000044, far 0xffffffffff700000 elr: 000000008085eb90 lr : 000000008085eb2c (reloc) elr: 00000000fff5fb90 lr : 00000000fff5fb2c x0 : 00000000fdef53a0 x1 : ffffffffff700000 x2 : ffffffffffae8000 x3 : 0000000000000000 x4 : 0000000000000000 x5 : 00000000fdef53a0 x6 : 0000000000000000 x7 : 00000000fdecedb0 x8 : 0000000000000004 x9 : 00000000ffffffd0 x10: 000000000000000d x11: 0000000000000006 x12: 0000000000000000 x13: 00000000fdecfd80 x14: 00000000ffffffff x15: 00000000fdece91d x16: 00000000fff5fbc0 x17: 0000000000000000 x18: 00000000fdee1d80 x19: 0000000000000000 x20: 00000000fdee57e0 x21: 00000000fffaf238 x22: 00000000fdecee00 x23: 00000000fdee5880 x24: 0000000000000008 x25: 0000000000000000 x26: 00000000800c0648 x27: 00000000800c0000 x28: 00000000800c0630 x29: 00000000fdeced90 Code: f9401001 8b020022 eb02003f 54fffec2 (b8004433) Resetting CPU ... resetting ...

此致、

Mari Tsunoda.

尊敬的 Mari:

您能否告诉我代码中具体更改了哪些内容、以便现在可以根据 DDR 配置文件自动调整 V2A_CTL_REG 值?

请参阅以下相关的 U-Boot 补丁。

这是来自 U-boot 的日志。 SDK 版本为10.00.[/QUOT]日志显示 U-Boot Detected 4GB DDR:

RAM 配置:

Bank #0:8000000 Bank #1:880000000

DRAM: 2GiB (有效4GiB)

Mari、您好、我同意 V2A_CTL_REG 值看起来不正确、如果看起来像这样:

V2A_CTL_REG (0x0F300020):

f1 01 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

值应为0x211。 这表示 SDRAM_IDX=16、REGION_IDX=17

这听起来在 SDK10中可以处理、但在 SDK9中、需要手动完成。 我的建议是直接在驱动程序中将其写入此处(摘自 Bin 发送的 https://git.ti.com/cgit/ti-u-boot/ti-u-boot/commit/?h=10.00.07&id=60502596e97be5191ccf6c805a141bad55cfaf7c 补丁链接

781 #ifdef CONFIG_K3_AM64_DDRSS

782 /* AM64x 仅支持最多2GB SDRAM */

783 writel (0x000001EF、ddrss->ddrss_ss_cfg + DDRSS_V2A_CTL_REG);

784 writel (0x0、ddrss->ddrss_ss_cfg + DDRSS_ECC_CTRL_REG);

785 #endif

进行以下更改

删除"#ifdef"行

-将0x211写入783行的 V2A_CTL_REG

执行后、通过读取 0x0F300020来确认寄存器是否正确

此致、

James