主题中讨论的其他器件:SysConfig

工具与软件:

您好、TI 专家 J ü、

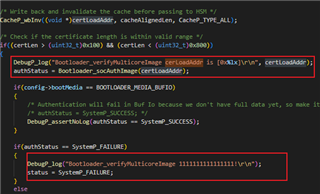

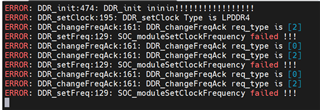

我们将使用 Samsung 的 DDR (4G K4FBE3D4HB-KHCT2V)替换 EVM 上的 DDR、将 生成的文件重命名为 board_ddrReginit.h、 并替换原始 board_ddrReginit.h.但 SBL 无法启动、如以下屏幕截图所示。 您能否帮助我确认这是不正确的参数配置引起的?

e2e.ti.com/.../j722s_5F00_board_5F00_ddrRegInit.h

此致。