主题中讨论的其他器件:TDA4VM

工具与软件:

尊敬的 TI:

关于将 PCIe 条映射到过程空间并对其进行访问后发生总线错误的问题、已经取得了新的进展。

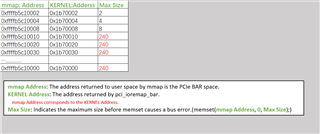

使用 gdb 调试时、我们发现每次执行汇编指令"str Q0、[x1]"时、都会发生总线错误、其中 x1 = 0xfff7f90028。 过程 mmap PCIe bar 后的地址是0xfff7f90000。 该地址似乎是8字节对齐的。 我不知道此汇编指令为什么会导致总线错误。 此外、在执行该指令之前、我已经检查了地址范围0xfff7f90000-0xfff7fA0000具有 RW-s 权限。

更令人困惑的是,当运行 Valgrind 时,没有发生总线错误,执行正常完成,结果检查中没有任何错误。 我想知道此问题是否与 PCIe 有关。 TI 专家能否对此提供帮助?

此致、

Qiang