请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VL-Q1 主题中讨论的其他器件:TDA4VL

工具与软件:

尊敬的专家:

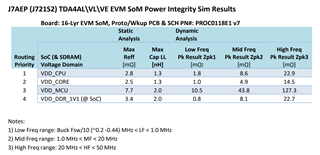

我们的客户正在进行 TDA4VL PI 仿真。 他们想知道以下结果是否考虑了 VRM 的影响? 如何设置 VRM 参数? 谢谢你

此致、

Zhu Xingyu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

VRM (稳压器)不是 PCB PDN PI 仿真的一部分。 VRM 和功率电感器应从仿真模型中"移除"、并且 应 按如下方式连接2个仿真端口:

跨连接 到被评估到 VSS 或 GND 的电源轨的 SoC 电源输入引脚。

2.在连接到被评估到 VSS / GND 的电源轨的 VRM 大容量电容器上。

在 PI 仿真期间、"PDN Bulk Cap Port"将短接、因为仿真"回顾 VRM 网络"由 PCB 布线和 PDN 去耦电容器(在仿真中、大容量电容和高频电容都连接到电源轨)构成、由 SoC 输入电源仿真端口。 这使 PI sim 能够仅评估 PCB 布局设计和 PDN 去耦方案阻抗与频率响应之间的关系。