主题中讨论的其他器件: SysConfig

工具与软件:

您好!

我们将 AM6421与 MCU+SDK _am64x_09_02_00_50搭配使用。

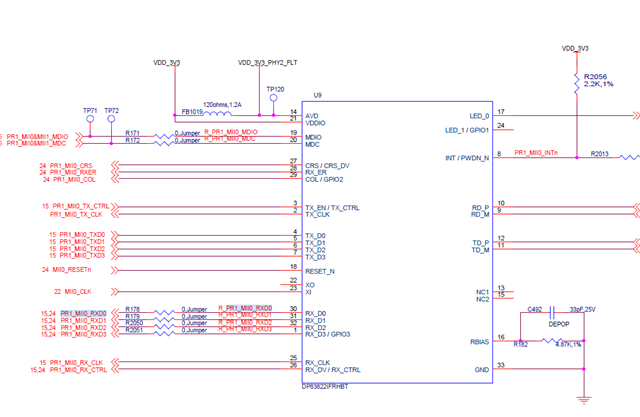

我们在定制板中使用了 DP83822 Phy。

我们已成功连接 ICSSG 端口、并测试了 RGMII 模式下的 DP8322 PHY。 我们在环回和外部 ping 中进行了测试、运行正常。

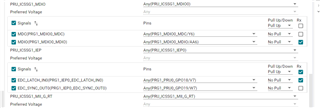

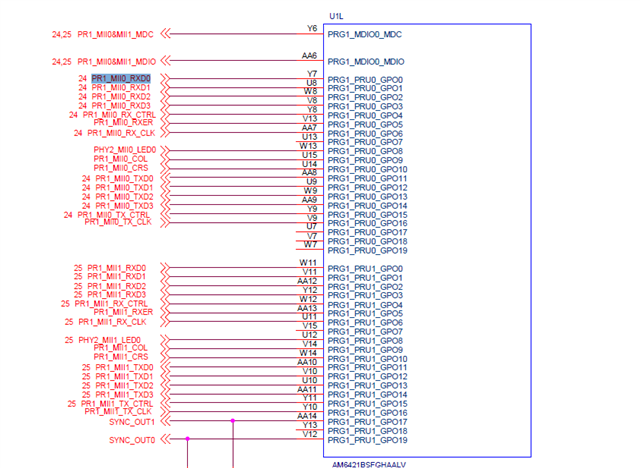

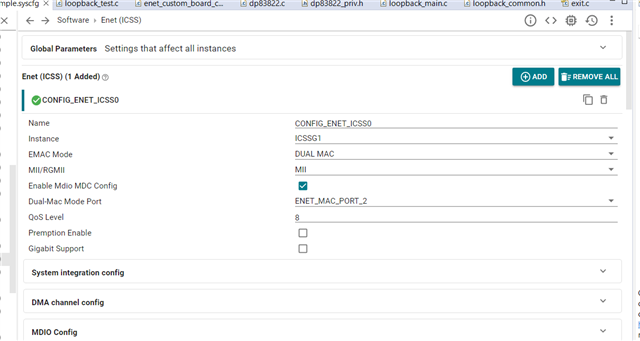

我们需要在项目中以 MII 模式工作、以便实现 Profinet IRT。 我们已 在 SysConfig 中将接口配置为 MII 模式、下面也附加了相同的配置。

DP83822配置为 MII 模式。 下面附加了寄存器转储。

我们需要您的支持来确定是否遗漏了在 MII 模式下运行 MAC 和 PHY 的任何配置。

我们无法 在 MII 模式下从 SDK 测试 enet_icssg_loopback_am64x-evm_r5fss0-0_nortos_ti-arm-clang 示例。

配置为 MII 模式后的 DP83822寄存器转储

PHY 2:配置后

PHY 2:BMCR[0x0]= 0x6100

PHY 2:BMSR [0x1]= 0x7849

PHY 2:PHYIDR1[0x2]= 0x2000

PHY 2:PHYIDR2[0x3]= 0xa240

PHY 2:ANAR[0x4]= 0x01e1

PHY 2:ANLPAR[0x5]= 0x0000

PHY 2:ANER[0x6]= 0x0004

PHY 2:ANNPTR[0x7]= 0x2001

PHY 2:ANNPRR[0x8]= 0x0000

PHY 2:CR1[0x9]= 0x0000

PHY 2:STS1[0xA]= 0x0100

PHY 2:PHYSTS[0x10]= 0x000c

PHY 2:BISCR [0x16]= 0x0140

PHY 2:1KSCR[0xF]= 0x0000

PHY 2:RCSR[0x17]= 0x0041

PHY 2:PHYCR[0x19]= 0x0022