主题中讨论的其他器件:SysConfig

工具与软件:

尊敬的 James:

客户的主板不稳定、几乎不能工作、有时在 U-Boot 中挂起、有时在 Linux 中随机挂起、

根据 AM62x DDR 布局指南、存在一定程度的布线长度违例、低8位布线过长、大于500ps*5mil。

| 影响 | |

| 高字节数据和 UDQS | 1500mil |

| 低字节数据和 LDQS | 3500mil |

| CLK P/N | 2170mil |

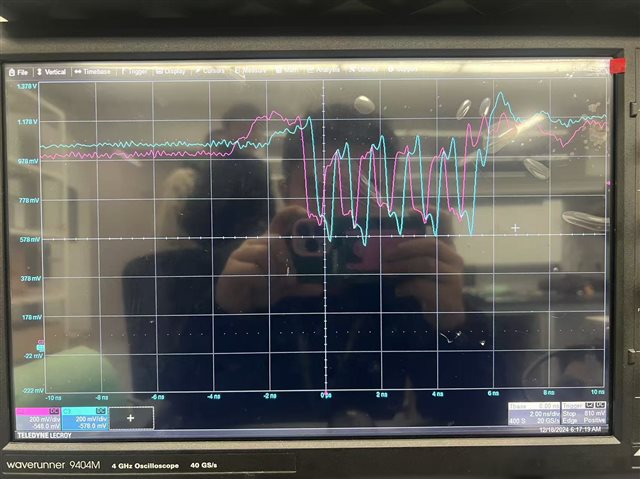

仿真结果如下:

问题:

#1。 布线长度是否会导致问题?

#2。 想要验证仅使用高8位且满足布局要求:SysConfig 中有仅8位配置选项、但默认为低8位、是否可配置为仅使用高8位?

#3. 是否可将其配置为补偿 PHY 寄存器中字节之间的延迟?