工具与软件:

你(们)好

我还有一个问题

以上内容是概要

|

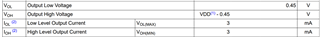

客户正在尝试将 LVCMOS 输出引脚与1.8VMODE 一起使用、但最大 vol 值为0.45V (IOL = 3mA)、这个值是一个高额定值、并且如果按照原样解释了电气特性、那么该设计不起作用。

然后我得到了如下答案。 只要 IOL 小于3mA、为 VOL 定义的最大限值就有效;只要 IOH 小于3mA、为 VIH 定义的最小限值就有效。 数据表指出、输出缓冲器能够灌入高达3mA 最小 IOL 电流的电流、低电平输出电压将保持小于为 VOL 定义的最大值0.45V、 输出缓冲器能够拉取高达3mA 最小 IOH 电流的电流、高电平输出电压将保持 大于为 VOH 定义的最小值(VDD - 0.45V)。 |

我知道 TI 的保证值在以上。

电路如何用作 LVCMOS 缓冲器?

如果连接了外部 PD 电阻器或输入缓冲器并且低侧 FET 导通、而 AM64输出为低电平、那么电流是否无法驱动?