工具与软件:

大家好、TI 团队:

TIDL 网络有23个输出测试器。

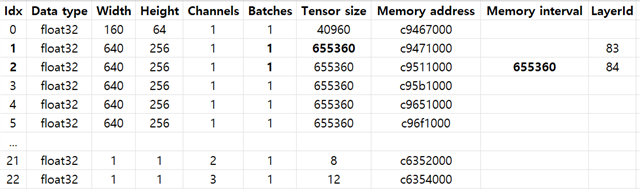

下图显示了输出密度的一些信息。

- IDX 1张张张张量在83层处理。

- IDX 2张张量在84层进行处理。

- 84层在83之前被处理。

我观察到 idx 2输出张量存储器在处理第83层后被入侵。

图层214的输出张量为 idx 1。

idx 1张量存储器大小与 idx 1和2之间的存储器间隔紧密相同。

在创建输出传感器时、我应该使用 outPadCh 吗?

为什么 TIDL 进程似乎使用超出分配的缓冲区大小的内存?

此致、

UK Lee