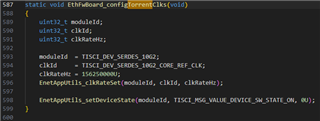

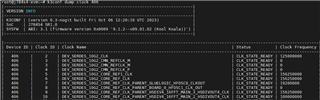

工具与软件:

您好!

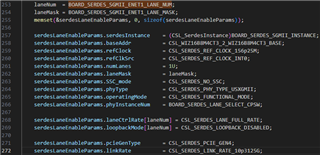

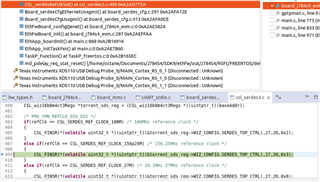

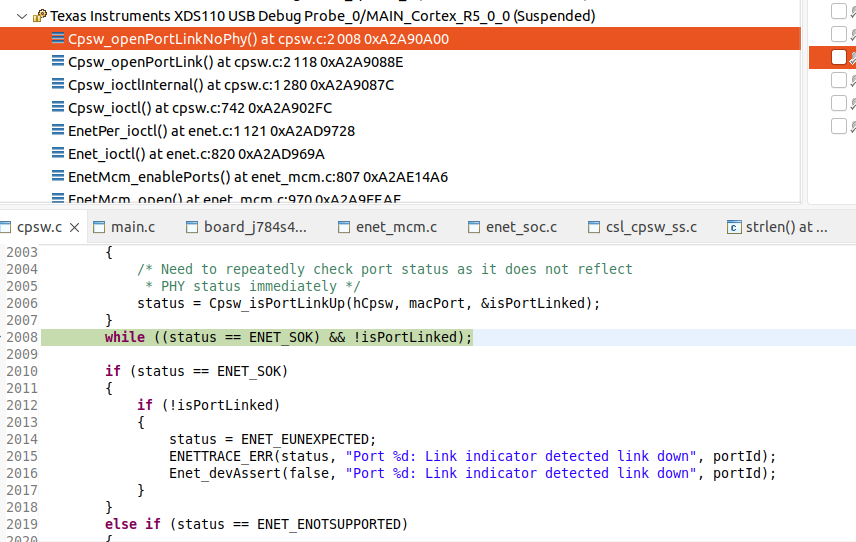

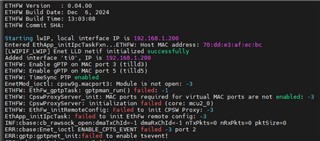

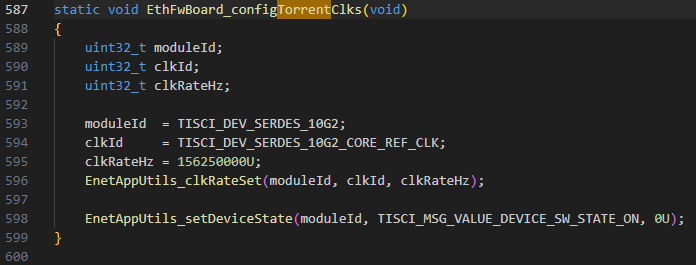

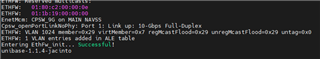

我要在 XFI 上使用10G、因为我要使用156.25MHz 的时钟频率。 建议使用外部时钟并使用 SerDes 2的通道2作为 XFI。 是否也可以从内部时钟获取156.25MHz 也是一种很好的方法。

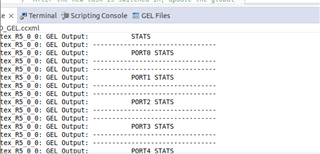

这是我到目前为止所做的:

- 。 k3-j784s4-exp1-exp2-usxgmii.dts 、我已将速度从5000更改为10000:

- &main_cpsw0_port1{

状态="正常";

PHY 模式="usxgmii";

MAC-ADDRESS =[00 00 00 00];

phys =<&phy_gmii_sel_cpsw0 1>、<&serdes2_usxgmii_link>;

PHY-names ="portmode"、"SerDes-phy";

固定链接{

速度=<10000>;

全双工;

};

};

- &main_cpsw0_port1{

- 还在 k3-j784s4-exp1-exp2-usxgmii.dts ,我检查了 serdes2 lane2被分配,正如我看到它被默认分配:

- &SerDes_ln_ctrl{

空闲状态= 、 、

、 、

、 、

、 、

、 、

、 ;

};

- &SerDes_ln_ctrl{

- 。 k3-j784s4-evm.dts 、我为 serdes2添加了一个节点、该节点包含我要使用的频率(156.25MHz):

- &serdes2_refclk {

时钟频率=<156250000>;

};*

- &serdes2_refclk {

- 。 k3-j784s4-main.dtsi ,我复制了什么存在的 SerDes 为 serdes2 :

- /{

SERDES2_REFCLK:SERDES-REFCLK{

#clock-Cells =<0>;

Compatible ="固定时钟";

};

};

- /{

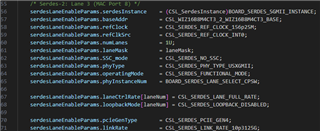

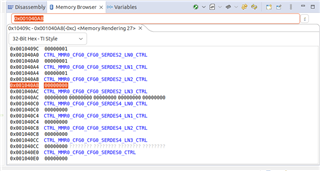

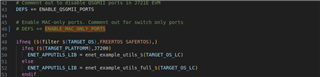

- 还在 k3-j784s4-main.dtsi、 我用&serdes2_refclk 替换了 &serdes_refclk、并将状态切换为"oke":

-

SerDes_fiz2:wiz@5020000 {

兼容="ti、j784s4-wiz-10g";

#address-cells =<1>;

#size-cells =<1>;

电源域=<&K3_PDS 406 TI_SCI_PD_Exclusive>;

时钟=<&K3_CLKS 406 2>、<&K3_CLKS 406 6>、<&K3_CLKS 406 5>、<&serdes2_REFCLK>;

时钟名称="fck"、"core_ref_clk"、"core_ref1_clk"、"ext_ref_clk";

num-channels =<4>;

#reset-cells =<1>;

#clock-Cells =<1>;

范围=<0x05020000 0x0 0x05020000 0x00010000>;分配的时钟数=<&K3_CLKS 406 6>;

Assigned-clock-parents =<&K3_CLKS 406 10>;状态="正常";

-

- 还在 k3-j784s4-main.dtsi 我还明白我需要使用&serdes2_refclk 在 assigned-clock-parents 中,但我不明白使用哪个 PLL :

-

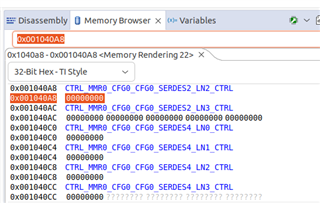

Serdes2: SerDes@5020000 {

兼容="ti、j721e-SerDes-10g";

REG =<0x05020000 0x00010000>;

reg-names ="torrent_phy";

重置=<&SerDes_wiz2 0>;

reset-names ="torrent_reset";

Clocks =<&SerDes_wiz2 TI_wiz_PLL0_REFCLK>、

<&SerDes_wiz2 TI_wiz_PHY_EN_REFCLK>;

时钟名称="REFCLK"、"phy_en_REFCLK";

分配的时钟=<&SerDes_wiz2 TI_wiz_PLL0_REFCLK>、

<&SerDes_wiz2 TI_wiz_PLL1_REFCLK>、

<&SerDes_wiz2 TI_wiz_REFCLK_DIG>;

ASSIGNED-CLOCKDNED =<&K3_CLKS 406 6>、

<&K3_CLKS 406 6>

<&K3_CLKS 406 6>;

#address-cells =<1>;

#size-cells =<0>;

#clock-Cells =<1>;状态="已禁用";

};

};

-

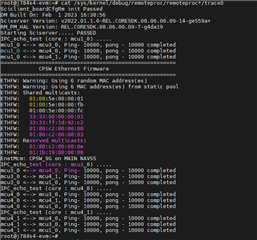

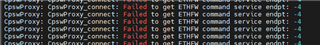

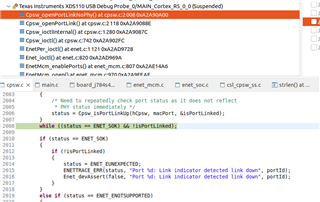

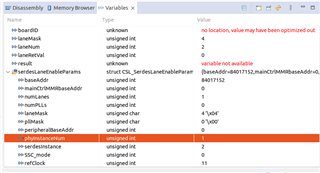

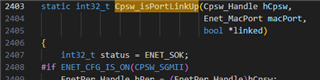

以下是我的问题:

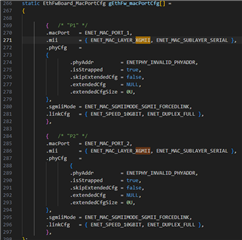

- 按照我刚才公开的方法、剩余的任务是在"assigned-clock-parents"字段中以红色分配&serdes2_refclk、这是正确的方法吗?

- 我们是否需要单独激活外部时钟? 我想应该在 u-boot 源码中激活它、您对它的激活过程有什么看法吗?

谢谢!

此致、

Wissam