工具与软件:

您好、专家

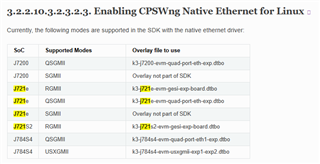

我之前在最新的 Processor SDK (10.01.00.04)中查看了用于 Linux 的 CPSWng 本机以太网的文档、发现 J721e SoC 仅列为支持 RGMII 和 QSGMII 切换。 提供了这些模式的覆盖文件(k3-j721e-evm-gesi-exp-board.dtbo和k3-j721e-evm-quad-port-eth-exp.dtbo)。 不过,这似乎是 SGMII 支持标记为"覆盖不是 SDK 的一部分"。

请您确认是否 J721e 在当前 SDK 中支持 SGMII MAC 端口? 如果不直接支持它、是否有任何未来支持计划、或者我是否需要自定义设备树和驱动程序来启用它?

提前感谢您的帮助!

BR

Jay