工具与软件:

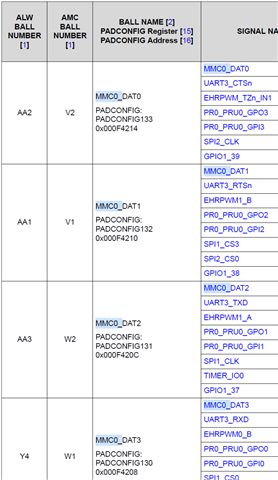

#1。 在使用 eMMC0引导的客户电路板上、没有上拉 eMMC0_DAT0、偶尔无法通过上电进行引导、但可以通过热复位或下电上电进行引导。

#2。 在 eMMC_DAT0上添加上拉电阻、到目前为止可以始终启动。

#3. 原理图检查清单需要在 eMMC_DAT 引脚上添加外部上拉电阻。

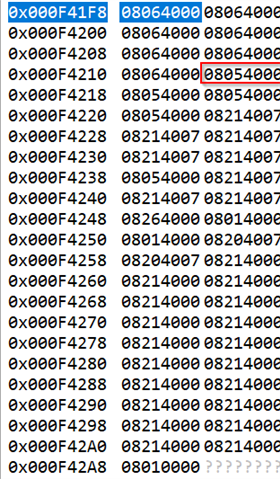

#4. 使用 JTAG 检查 AM62-SK 电路板、发现 eMMC0_DAT0、eMMC0_CLK 和 eMMC_CMD 拉电阻未启用。 但其他数据引脚(eMMC_DAT1-7)已启用上拉。

问题:为什么不上拉 eMMC0_DAT0?

BTW、CAN 探测 eMMC0_DAT0上的信号、尽管引导失败。 (引导失败不会在 UART 上输出日志、协商后应该会在某个位置停止、因此与 DDR 配置无关)