工具与软件:

JJJD、您好!

我们已经对 AM62Px 设计进行了仿真。 我们的原理图和布局遵循 SK-AM62P-LP: CK 和 ADDR_CTRL - 当所有组信号都路由到同一层上且 CA/CKE/CK 信号的 T SPLIT 部分位于附加层时、其路由采用 T 拓扑。 CS0_A、CS1_A、CS0_B、CS1_B 的拆分方式与 EVK 布局/原理图中不同。 布局实现与 EVK 中的实现相同。 所有组信号都匹配为0.1ps。

我们仿真了3733MTS、结果显示 CS 信号没有通过眼图、但是 CS 信号与 CK 时钟同步。 (请注意、它们的振幅也不同、因为它们具有 PD 上述线程中建议的80 Ω PU/FET)、

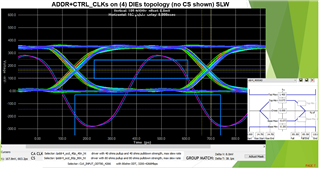

移除 CS 信号后、眼图就清晰了。 参见以下图片

我的问题是:

1.所示的 CS 信号是否令人满意?

2. CS 信号是否 也能满足眼图要求? (据我所知、它们是控制信号、运行频率低于 CK/CA 信号)。

3.由于 CS 信号已经与 ADDR/CK/CKE 匹配了0.1ps、我们是否应该添加延迟以使其与组中的其余部分对齐? CS 信号允许的最大偏斜是多少?

4. CS 信号的上升时间似乎比其他组信号更快、这可能是由于其他信号中额外的覆铜也通过了 T SPLIT。 在这方面是否需要采取任何行动?

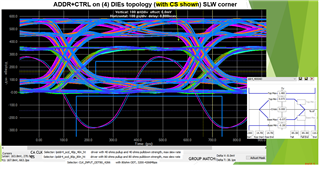

第3季度:我们测试了一个延迟,现在 CS 与 ADDR/CKE 信号更加一致(见下文)。 请告知是否首选此修改:

感谢您提供有关这些信号仿真的任何额外输入。

感谢您的建议、

John