工具与软件:

您好!

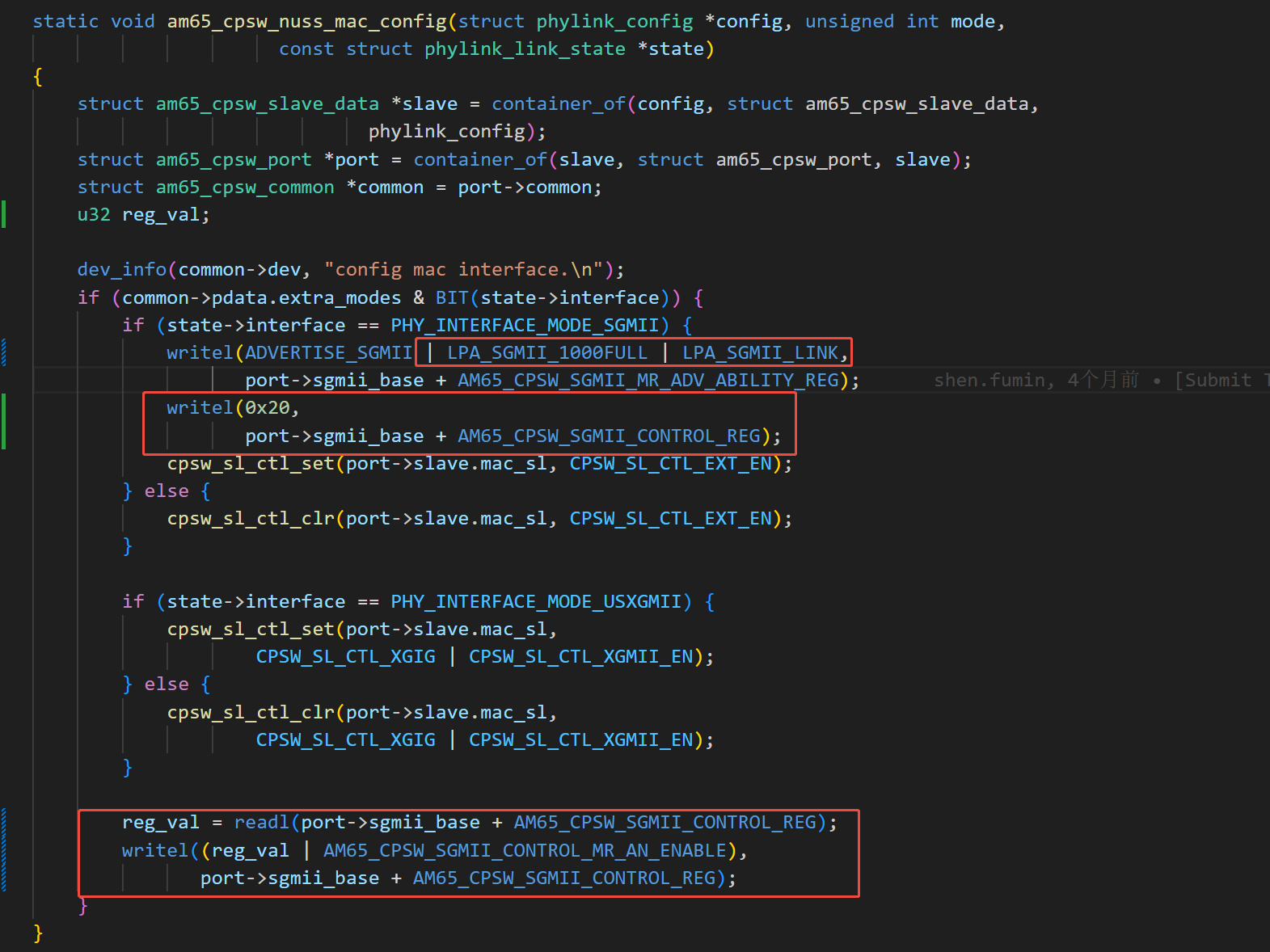

由于没有足够的硬件端口用于使用、我们必须混合 cpsw5g 的 RGMII 和 SGMII 端口、端口1、3和4是 SGMII 端口、端口2是 RGMII 端口。 由于与 EVM 不同、我们将一些配置代码从 qsgmii 配置为 SGMII。 但该函数将 CpswMacPort_isSgmiiSupported 置为有效并显示"SGMII 端口未就绪、SERDES PLL 未锁定"。

因此我检查了 CPSW0_SGMII 寄存器、例如、 CPSW_SGMII_IDVER_REG_0具有非零值(0x4EC21102) 、但 CPSW_SGMII_IDVER_REG_1、CPSW_SGMII_IDVER_REG_2 、CPSW_SGMII_IDVER_REG_3的 内容都为零、因此检查功能失败。

此外、是否有 我们的自定义用法手册(不适用于 qsgmii 端口)? 谢谢