请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DRA821U-Q1 主题中讨论的其他器件:DRA821

工具与软件:

您好!

您能否提供内存控制器交流时序规格?

谢谢

最大值

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

您能否提供内存控制器交流时序规格?

谢谢

最大值

尊敬的 Max:

您能否提供 LPDDR4存储器控制器交流时序规范?

我们不提供 DDR 子系统的交流时序规格。

我们建议您遵循我们的 LPDDR4电路板设计和布局布线指南(下面的链接)。

https://www.ti.com/lit/pdf/spracn9

此致、

Kevin

尊敬的 Kevin:

是的、我们遵循了布局指南、我们也选择了 SI。

我们查看了 spracn9f.pdf、

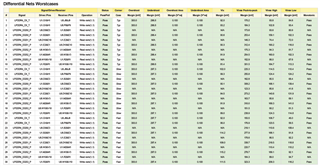

下面是关于我们对内存控制器时序参数的使用情况的建议:

BTW、如何将文件(PDF)附加到 TT?

谢谢

最大值

尊敬的 Max:

SOC 文档提供了可读取的 soc 眼图使用值、但表明眼宽非常大(0.7 UI)。 如果将其与存储器器件输出延迟的不确定性(0.3UI)结合使用、则无法满足裕度(例如0.3UI+0.7UI = 1 UI)、因为信号转换、抖动等的裕度将为0ps、…。0.7UI 是否正确?

是的、我的理解是0.7 UI 是正确的。 掩码很大、因为它需要考虑 IBIS 仿真中未包含的任何内容。

您提到针对输出延迟的不确定性添加0.3 UI、但我的理解是您应该不需要添加0.3 UI。

如布局指南的示例(图3-5)所示、使用0.7 UI 读取数据掩码时有裕度。

[报价 userid="419570" url="~/support/processors-group/processors/f/processors-forum/1462497/dra821u-q1-dra821u-q1-SOC-LPDDR4-memory-controller-ac-timing-sepcifation/5612047#5612047"]此外、soc 规范显示了典型的 RX 数据掩码(菱形而非矩形)、您是否采用矩形?否、我们仅提供菱形面罩进行读取。

此致、

Kevin