主题中讨论的其他器件:AM68A

工具与软件:

您好!

我目前正在使用 TIDL (SDK v10.00.08)在 AM68a 电路板上配置自定义神经网络。 我注意到、在模型工件生成期间、创建了两个 csv 文件(请参阅附带的屏幕截图)、其中 每层的运行时间不同、但存储器占用空间类似。 这两个文件的区别是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我目前正在使用 TIDL (SDK v10.00.08)在 AM68a 电路板上配置自定义神经网络。 我注意到、在模型工件生成期间、创建了两个 csv 文件(请参阅附带的屏幕截图)、其中 每层的运行时间不同、但存储器占用空间类似。 这两个文件的区别是什么?

你好,谢谢你的答复,

我注意到这两个文件的内容有两个主要区别,如下所示:

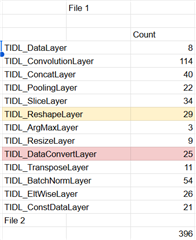

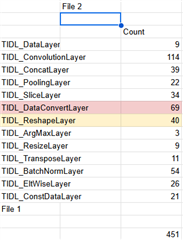

-两个文件中的整形和数据转换层的数量不同:这是否表明 TIDL 在网络上执行一些优化以减少这些层的数量? (屏幕截图1和2)

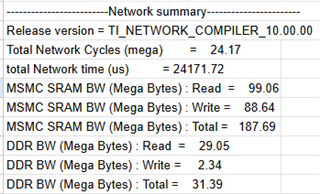

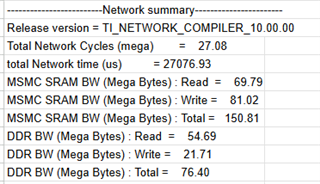

-第二个文件中 MSMC SRAM BW 的大小较小(即:减少层数),但总运行时间略高。 我的问题是,如果我们假设一个优化策略是什么差异的两者,是否可以禁用此优化以保持运行时间最小? (屏幕截图3和4)

是否可以访问编译器文档以进一步了解在后台运行的优化类型?

屏幕截图1:

屏幕截图2:

屏幕截图3:

屏幕截图4:

Mehdi 先生阁下;

我已经向同事询问过这个问题(发布编译文档)。 目前我们还没有发布任何类似的东西。 但是、我将询问开发/工具团队这是不是未来对此有任何计划。

同时、您可以在该链接中找到 TIDL 文档。

https://github.com/TexasInstruments/edgeai-tidl-tools/tree/master/docs

我现在将关闭该工单。

但如果您有其他问题、可以随时提交一个新问题。

谢谢。此致

文立