工具与软件:

大家好、tda4vm-sdk10.1网络的部署揭示了存储器输出偏移问题。

有关的现象 :模型输出正确的 PAD 和 channelPitch 信息,但在 writeTIDLOutput app_tidl_module.c vision_app 中使用图像保存功能时,查看时会出现偏移。 请参考下面的两张图片。 以前解决 entry-sdk10.0中类似问题的修补程序不适用于 VM-sdk10.1或此特定模型。

补丁和结果显示 :如下,您可以帮助同步调试吗?

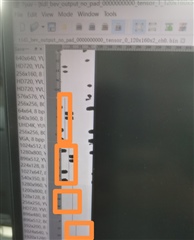

错误现象、图1 :

[不包含图像]

错误现象、图2 :

[不包含图像]

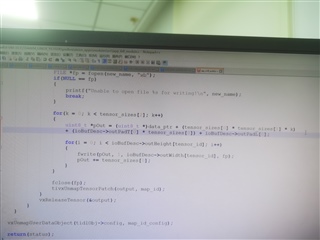

entry-sdk10.0中类似存储器偏移问题的上一个补丁、图3 :

[不包含图像]

网络模型 : pModel.bin 和 pModel_io_1.bin 是虚拟机的模型、带有 RTOS 10.01.00.04的 SDK 版本。

网络输入 : input_50_0.rgb、二进制文件输入。

网络输出 :可在8bpp 模式下查看7yuv、宽度120和高度160 (键盘宽度为121)。 可视化后、会观察到以下误差:

tidl_bev_output_no_pad:表示已删除无效区域的张量,但有效区域内仍然存在偏移,并伴有黑色垂直条。tidl_bev_output_with_pad:表示完全保留带黑点和白点无效区域的张量内存,并且在有效区域内有一个偏移,并伴有黑色垂直条。

尝试使用运行此模型 TI_DEVICE_armv8_test_dl_algo_host_rt.out、但输出中没有内存偏移。 怀疑 tidl_RT 更新中的某个位置没有更新 vision_app 测试用例或 app_tidl_module。 请提供一个补丁、谢谢!

所有输入和输出资料均在 e2e.ti.com/.../model_5F00_in_5F00_out.zip 中提供model_in_out.zip。