主题中讨论的其他器件:AM62P

工具与软件:

尊敬的 TI:

我有2个与 AM62A 平台上的安全代理配置和 HSM 相关的问题:

-

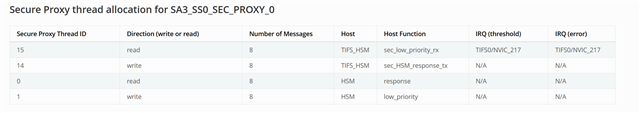

在的安全代理线程分配表中

SA3_SS0_SEC_PROXY_0、列出了 TIFS_HSM 和 HSM 的线程 ID、但在与 HSM 内核通信时、我找不到 DM 内核、MCU 内核或内核的线程 ID。

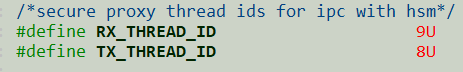

同时、该

hsm_ipc演示定义RX_THREAD_ID为9和TX_THREAD_ID8。

使用这些宏定义访问 sproxy 寄存器会导致硬中止。 这些 ID 是另一个映射表的一部分吗? 如果是、您能否说明我可以在哪里找到该分配?

-

在表中、 TIFS_HSM 作为主机被列为

sec_low_priority_rxsec_HSM_response_tx线程和线程。 为什么两个 TIFS_HSM 内核一起用作主机?

此致、

Yang