工具与软件:

您好!

我的配置过程和设置与我之前的论坛帖子相同: https://e2e.ti.com/support/rf-microwave-group/rf-microwave/f/rf-microwave-forum/1452860/afe7950-4t4r2f-8b10b-2-4576-gbps-config-not-synchronizing :

JESD204B、8b10b SERDES

4 Rx

2 FB

4个发送

ADC fs = 2949.12、 抽取因子为48

ADCFb FS = 2949.12、 抽取因子为24

DAC FS = 11796.48、内插96

串行器/解串器速率= 2457.6.

使用 AFE7950EVM 板载振荡器/PLL

更新了 jesd_link_params.vh 以匹配配置和 ZCU102 SERDES 映射

尝试按照 TI204c-Setup.docx 启动设计后、我将遵循以下操作顺序:

- 打开 ZCU102电源

- 打开 AFE7950EVM 的电源

- 打开 Latte

- 运行 setup.py

- 运行 devInit.py

- 运行4T4R2F_2p4576.py

- 对 FPGA 进行编程

- 释放 MASTER_RESET_n -> 1

- 释放 TX_RESET -> 0

- 运行 ConfigAfe.py

- 释放 RX_RESET -> 0

我有时只能使 JESD 链路双向同步、我通常需要发出一个或多个 Latte JESD 重新同步命令(TI_IP_AfeJesdReSync.py)、并使用 VIO 模块将 FPGA 复位一次或多次。

我将 AFE7950EVM 连接到 Xilinx ZCU102开发板的 J4时进行设置。 源基准代码为 TI 参考设计:C:\Users\jhobart_reliate\Downloads\TI_AFE7950\TI204C-IP-Release-v1.12-Latest\reference_designs\zcu102_8b10b、TI204C-IP-Release-v1.12-Latest\TI-204C-CoreIP\Vivado_2022_and_new\RTL\TI_204C.SVP、修改了以下参数:

184.32 MHz

SYS_PLL 输出184.32 MHz sys_clk 和30.72 MHz mgt_freerun_clk

管理速率2.4576 Gbps

我修改了 jesd_link_params.vh、使 zcu102到 afe7950evm 接口与 F、K 值匹配、以匹配我的配置。

我的 jesd_link_params.vh、约束条件和脚本文件已随附。 请告诉我、在此设计中、将 RESET 取消置位时是否需要考虑其他因素。

e2e.ti.com/.../files_5F00_e2e_5F00_1452860.zip

在 TI_IP_ConfigAfe.py 之后: ###########Device DAC JESD-RX 0 Link Status###########

lane0 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane1 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane2 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

lane3 Errors=0b1111; Got errors: 8b/10b disparty error; 8b/10b not-in-table code error; code synchronization error; elastic buffer match error. The first no-/K/ does not match 'match_ctrl' and 'match_data' programmed values;

CS State TX0: 0b10001001 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

重新同步没有帮助、因此我将 FPGA 恢复到复位状态(MASTER_RESET_n=0、TX/Rx_SYNC_RESET=1)并再次运行配置:

###########Device DAC JESD-RX 0 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 0

###################################

###########Device DAC JESD-RX 1 Link Status###########

CS State TX0: 0b10101010 . It is expected to be 0b10101010

FS State TX0: 0b01010101 . It is expected to be 0b01010101

Could get the link up for device RX: 1

###################################

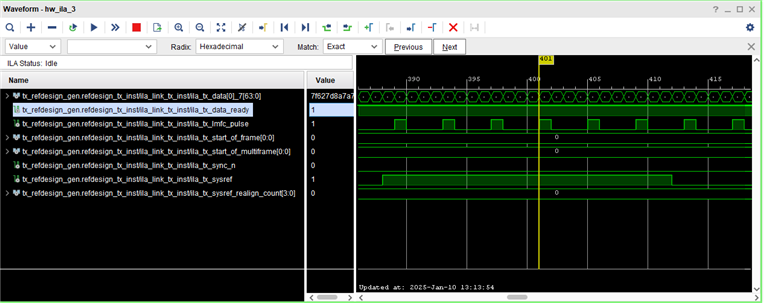

然后、我将 Rx_SYNC_RESET 设置为"0"、但 Rx_lmfc_to_buffer_release_delay[9:0]不会更改值、并且 Rx_LANE_DATA_VALID 始终为低电平。 我再次切换了 Rx_SYNC_RESET 几次、最终看到 Rx_LANE_DATA_VALID 开始切换。

注意: 在两个方向上建立链路后、JESD 链路保持稳定。

任何想法都将受到赞赏。 我将重点介绍慢的 mgt_freerun_clock、然后查看是否使用较慢的时钟意味着我需要以不同的方式处理复位。