工具/软件:

您好、David:

对迟来的答复表示歉意。 "PLL2被锁定"LED 亮起;但是、在芯片示波器中、在将 MASTER_RESET_n 置为无效后、qpll0_LOCKED 值不会变为3 我们有2个关键问题;首先、我们希望确认发光的 LED 是否明确表明 PLL2已锁定、或者尽管 LED 亮起、但芯片示波器中是否仍然存在导致问题的问题? 此外、由于我们使用默认脚本和提供的文件、我们是否应该检查或修改任何特定参数来解决此问题? 感谢您的帮助。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、David:

对迟来的答复表示歉意。 "PLL2被锁定"LED 亮起;但是、在芯片示波器中、在将 MASTER_RESET_n 置为无效后、qpll0_LOCKED 值不会变为3 我们有2个关键问题;首先、我们希望确认发光的 LED 是否明确表明 PLL2已锁定、或者尽管 LED 亮起、但芯片示波器中是否仍然存在导致问题的问题? 此外、由于我们使用默认脚本和提供的文件、我们是否应该检查或修改任何特定参数来解决此问题? 感谢您的帮助。

您好、David:

感谢您的答复。 我们测试了 R309处的122.88 MHz 晶体振荡器和 C275 (1474.56 MHz)附近的 LMK 时钟、并以-45.16dBm 的极低功耗获得正确的 LMK 时钟频率、如下所示。 请告诉我们这是否是预期行为、如果不是、可能是什么原因导致此类衰减。

我们还观察到每次下电上电时 qpll 锁定行为的变化。 在某些情况下,qpll 会立即 锁定,但在下一次下电上电时它不会锁定,或者有时锁定时间过长,甚至在锁定和解锁状态之间波动。

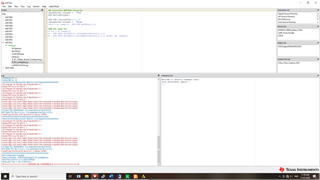

在这种情况下、qpll 已为我们锁定、Latte 控制台中出现相应的错误:

在这种情况下、qpll 已锁定但随后再次解锁、以及运行 AFEConfig.py 脚本时 Latte GUI 中的相应错误:

无论芯片示波器中的 qpll 是否锁定、LMK PLL 都会锁定且时钟正确提供。 我们的问题之一是、由于 qpll 未锁定会由于 GT 中的四通道未接收到正确的时钟而导致 SERDES 通道错误、但我们不确定如何在我们的 FPGA 上检查该问题。 您能否向我们说明对 VIO 信号(qpll0)进行编程以锁定和更改其值时背后的逻辑?

感谢您的帮助。

您好、David:

好状态和坏状态之间没有明显的功率差异。 在具有1474.56MHz 的 C275下、二者的功耗都在-43dBm 和-45dBm 之间。

我们观察到、根据参考原理图、从 LMK 生成 FPGA 时钟输出线上的唯一电阻器是 R353或 R357处的零电阻器或'DNI'。 那么、我们究竟在哪里探测 FPGA 时钟呢?

此外、如您所述、QPLL0锁定信号来自 Xilinx 收发器、并指示收发器 PLL 锁定到传入的时钟。 如果没有正确设置该信号、则这确实表明四倍收发器的时钟存在问题。 您能否建议我们进行任何校正以确保正确设置? 我们用于探测时钟的示波器适用于高达3.5GHz 的频率。 这应该是足够的权利吗?

您能否也仔细阅读我们的脚本、并确认根据我们的规范、这些脚本是否正确?

您好、

这里可能有一个错误。 在 C273和 C275上、您不应看到1474.57MHz 时钟。 您应该看到一个184.32Mhz 时钟、该时钟是 FPGA 设计所需的频率。 如果您在这些引脚上看到1474.56Mhz 时钟、则 LMK 配置可能存在问题。 您是否使用 AFE79xx GUI 为 LMK 生成了寄存器写入? 如果不是、我建议使用它来生成一组新的 LMK 寄存器写入。

关于收发器设置、我确实在物理资源页面中看到了一个小问题、应将库129的参考时钟源设置为使用库130的时钟、因为 FMC 连接器上的时钟仅路由到库130。

此致、

David Chaparro

您好、David:

我们仅按照 TI204C 设置文件中给出的步骤使用 AFE79xx Latte GUI 来配置 LMK、并在多次下电上电后评估了电路板。 情况仍然如此,在有些情况下 qpll 立即锁定,但在下一次下电上电时它不会锁定或锁定需要太长时间,有时甚至在锁定和解锁状态之间波动。 在它锁定的情况下、RX 和 TX 工作正常、但在测试一段时间后相同的通电状态下、qpll 突然再次解锁。

我们最初设置了库129的参考时钟源、以便仅使用库130的时钟、并观察到相同的行为。 您请仔细检查我们的 LMK 脚本、确保脚本没有问题、可能导致寄存器写入存在差异、从而导致出现错误的时钟、您能否确认应将哪些值写入寄存器地址、以便我们可以与日志进行交叉检查。

您好、

测得的时钟仍然存在问题、因为它应该是184.32MHz。 如果将频谱分析仪中心频率移至184.32MHz、是否会看到振幅更高的时钟?

我相信前面已经被问及这一点 、但我想仔细检查一下、这两种状态之间5V 电源上的 EVM 电流消耗是否有任何变化?

您是否能够在电路板或 FMC 连接器上看到任何损坏? FMC 连接器是否完全按压到 ZCU102上以确保最佳连接?

可以完成的一项测试是使用另一个 FMC 连接器更新工程。 这将告诉我们是 AFE EVM 出现问题、还是该特定 ZCU102 FMC 连接器上的信号出现问题。

此致、

David Chaparro

您好、David

我们需要确认、这两种状态之间的 EVM 电流消耗没有明显的差异、并且我们无法在电路板或 FMC 连接器上看到任何损坏。 我们确保充分按下 FMC 连接器以确保实现出色连接、甚至通过更改 FMC 端口进行了测试。 然而、我们没有观察到 qpll 的行为发生变化、该变化随着下电上电而继续变化。

我们也希望您能提出任何关于我们可以寻求解决此问题并推进我们的项目的替代方法或材料的建议。