Other Parts Discussed in Thread: AFE7950

工具/软件:

TI 团队大家好、

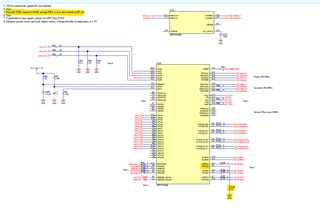

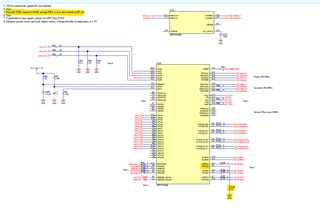

相对于 AFE7950IALK、FBTDD2 引脚连接到 RF_OUT?

正如我们看到的航天级原理图所示、该引脚未连接到 RF_OUT、因此必须在设计中将其拉低。 (请检查随附的卡扣)。

但由于 AFE7950 具有多个 EVM、因此在其他设计中并非如此、除了航天级设计外、FBTDD2 引脚可以由 FPGA GPIO 控制。

请准确建议 AFE7950IALK 必须遵循的内容

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: AFE7950

工具/软件:

TI 团队大家好、

相对于 AFE7950IALK、FBTDD2 引脚连接到 RF_OUT?

正如我们看到的航天级原理图所示、该引脚未连接到 RF_OUT、因此必须在设计中将其拉低。 (请检查随附的卡扣)。

但由于 AFE7950 具有多个 EVM、因此在其他设计中并非如此、除了航天级设计外、FBTDD2 引脚可以由 FPGA GPIO 控制。

请准确建议 AFE7950IALK 必须遵循的内容

尊敬的 Garima:

AFE 具有许多 GPIO 引脚、可通过配置来支持任何受支持的 GPIO 功能、其中一个是 FBTDD2。 如果未连接特定引脚(例如上述电路板上)、则可以将该功能分配给连接到 FPGA 的 GPIO 引脚。

如果您需要控制此 GPIO 功能、则可以将其连接到 FPGA 或将其分配到连接到 FPGA 的 GPIO、请注意、也可以使用 SPI 写入来覆盖 GPIO 功能、因此如果您想保存引脚、则无需连接。 使用 SPI 命令的唯一缺点是所需的时间将取决于所有寄存器写入所需的时间。

此致、

David Chaparro