您好!

我们在电路板中安装的 AFE7444配置方面遇到一些问题、但根本原因尚未完全消除。

为了进行调试、我们设置了使用由 TI GUI (Mode6)控制的 EVK FTDI (来自 J13引脚1、4、7和10)来配置器件的可能性。 在这种设置下、器件正常工作(在 TX 和 RX 链上)。

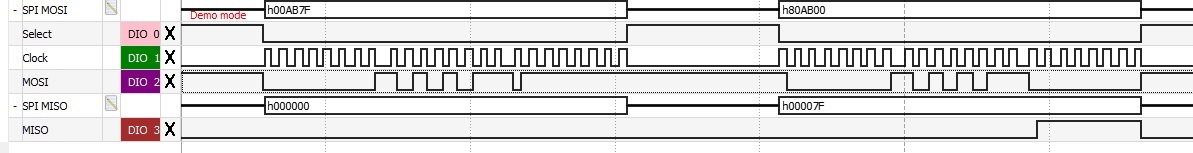

当 SPI 由板载处理器控制时、会发生此问题:我们使用的驱动程序不支持24位访问、因此我们实现了8+8+8位访问、如图所示(50us 时间标度、200kHz 时钟)。

为了进行调试、我们在每次写入访问后读回寄存器值、并且不会出现任何不匹配情况、除非是部分只读的寄存器。

要设置寄存器、我们将解析从 GUI 生成的配置文件(logfile_conved_to _low_level_read.cfg、已连接)。/CFS 文件/__key/communityserver-discussions 组件-files/220/logFile_5F00_converted_5F00_to_5F00_low_5F00_level_5F00_read.cfg

请注意、您是否认为当前实施(3倍8个时钟周期)可能会影响配置的可靠性?

从我们测量的 EVK 来看、在每次寄存器访问之间、最小延迟为30ms、是否严格要求该延迟才能获得正确的配置?

提前感谢您的支持

此致

Massimo