请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE7900EVM 主题中讨论的其他器件: AFE7950EVM

您好!

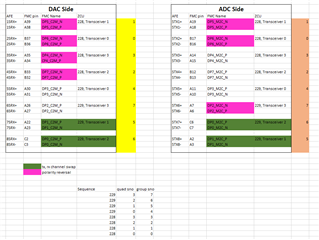

1) 1)在 ADC 接口(STX)中、有3个极性反转的差分对、但在代码中、反转的是4对

2) 2)是否可以请您帮助我们了解极性反转的语法?

3) 3)在 Vivado 代码中、接收和发送的数据为 rx_lane 数据和 tx_lane 数据。 与以前一样、该数据是否与 mgt_rx_usrclk2同步? 现在是(122.88 x 2 = 245.76 MHz)吗? 由于我们使用 RxA 和 RXC、因此 RxA 和 RXC 对应的线将为 RX_lane 数据[0]、RxA 对应的 RX_lane 数据[1]和 RXC_lane 数据[4]和 RXC 对应的 RX_lane 数据[5]。 对于 TxB、它将是 TX_lane 数据[2]、TX_lane 数据[3]和 TxD、它将是 TX_lane 数据[6]和 TX_lane 数据[7]。

4) sys_clk 和 REFCLK 是否为122.88MHz (根据约束文件中的注释、它为156.25MHz、但计时约束和 PLL 设置本身适用于122.88MHz)?

5) 5)请告知如何实现确定性延迟以及该延迟的数量是多少(通道 RxA + TXB 和 RXC + TXD 之间的延迟? 请针对相同的测量设置提供建议。 此同步引脚是否需要单独的同步引脚或由 sysref 负责处理?

6) 6)我们有两种设置:一种是 AFE7900EVM、另一种是 AFE7950EVM。 在 AFE7950EVM 中、我认为所有通道都是相同的、因此无需修改42220的前端、我们将使用它在10GHz 下进行测试。

请告知 AFE7900EVM 在以下频段进行测试所需的更改:

1) 3.5至4.5GHz

2) 5GHz

7) 7)由于我们需要自行设置 Tx 和 Rx NCO 频率、因此请建议如何计算不同 NCO 值的寄存器值。 我假设这些模式与模式无关(42220或 DAC 和 ADC 采样频率保持不变的任何其他模式)。

谢谢、