主题中讨论的其他器件: LMK04828、 DAC38RF83

您好!

我参考本文档第14页的第7.4节:

它提到使用一个 SYSREF+上具有1150欧姆上拉电阻和 SYSREF-上具有453欧姆下拉电阻的网络来在不驱动 SYSREF 时创建一个固定的 VOL。

我想确认、这不是向后的吗? 如果您要上拉 SYSREF+而您要下拉 SYSREF-、这是否会在输入端产生正差分电压为+至-的 VOH 场景? 这是否会使 SYSREF 输入保持"有效"或逻辑高电平? 为什么不执行反向、将 SYSREF-拉至 SYSREF+上方以使 SYSREF 差分输入保持在逻辑低电平偏置、或在未置状态下在+至-之间的输入上使用负差分电压?

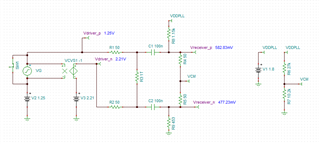

我已为 SYSREF 设置了具有~2.2V 共模和~0.75V 至1.2V 差分摆幅的驱动器、因此我认为需要使用交流耦合方法作为电阻分压器、将共模电压降至0.5V (DAC38RF89的 SYSREF 输入共模规格) 会导致过多的信号衰减