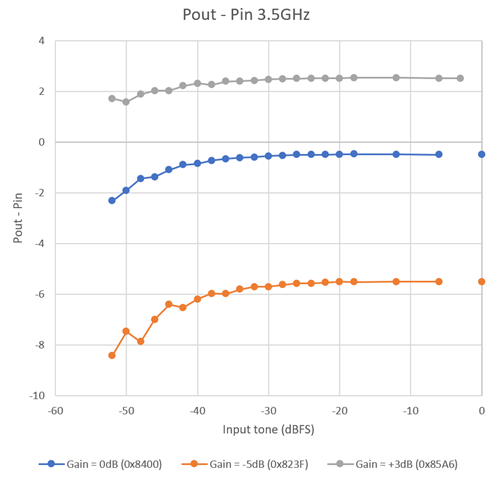

附加的输入到输出增益测试结果与非线性相似。

请告诉我非线性的原因。

我假设输出增益是恒定的、因为不使用输入增益调节。

但以下测试结果是更改输出增益。

我想知道这些结果取决于 DAC38RF80规格或外部问题。

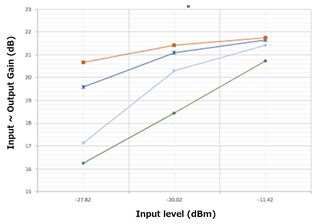

※橙色:10dB、蓝色:5dB、浅蓝色:0dB、绿色:-5dB

请参阅下面的测试条件;

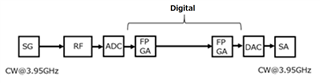

・信号发生器(SG)输出 CW:3.96GHz

・DAC38RF80接收来自 FPGA 的信号、并在频谱分析仪(SA)上确认 DAC 输出信号。

・Ω 在上述条件下、在输入电平和 DAC 增益变化的条件下测得的 DAC 输出增益。

(DAC 增益设置为10dB、5dB、0dB 和-5dB)

此致、

Satoshi