主题中讨论的其他器件: ADS54J60

你(们)好

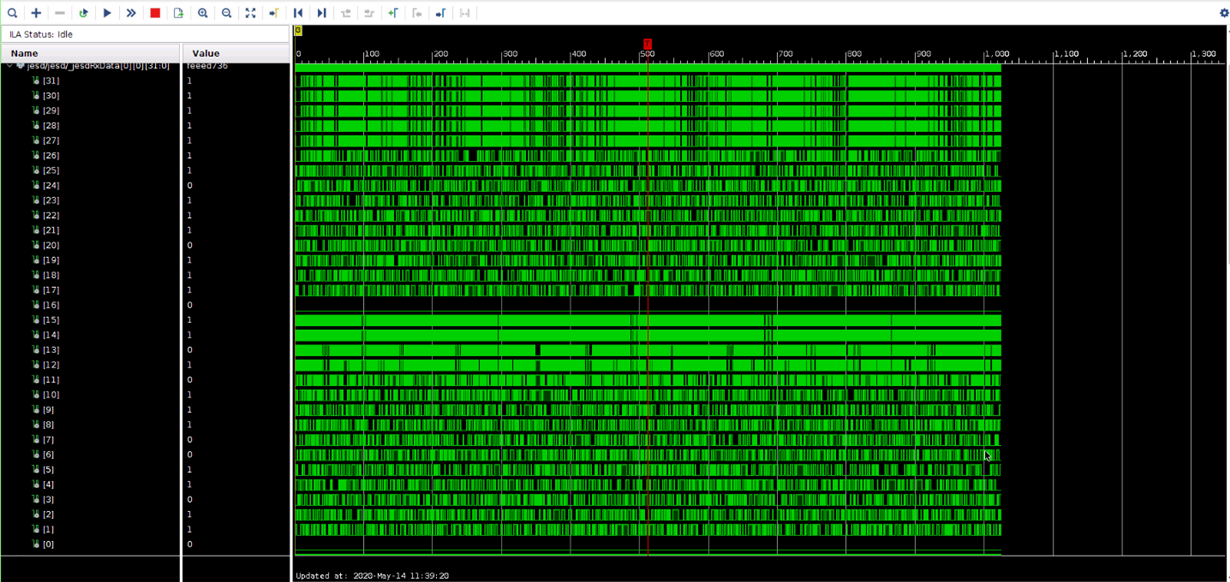

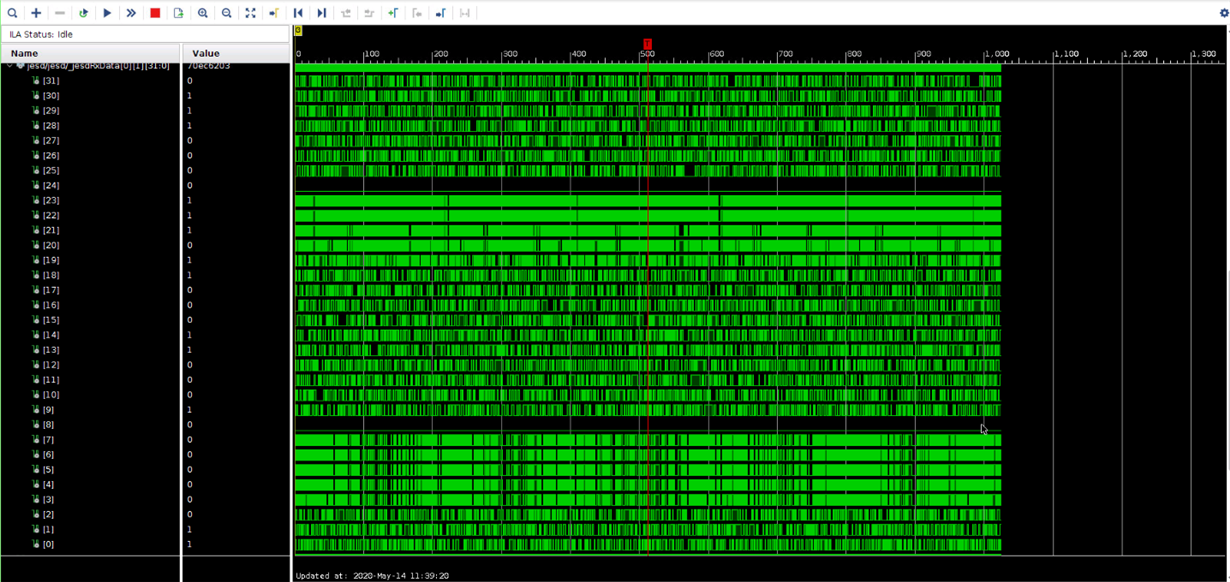

我看到、FPGA 以相反的顺序接收 ADC 中某些通道的 JESD 数据。

即、对于某些通道、数据为 B15 - B0、而对于某些通道、数据为 B7-B0;B15-B8。

当我执行 JESD 复位时、这会发生变化。

即、按照 B15-B0顺序接收位的通道可以更改为 B7-B0;B15-B8、反之亦然。

随附的 FPGA 捕获显示了 order.e2e.ti.com/.../ADS58J63_2D00_MSB1.cfg 的位打包

在这两种情况下、JESD 链路都是稳定的。

请告诉我这种行为的发生原因。

我已附上我的 ADC 配置供您参考。 下面是 ADC 的主要设置。

ADC 模式:模式0

LMFS:4841

采样率:500MHz

DDC:是、Fs/4

如果您需要更多信息、请告诉我。