您好!

我想确认 DAC38RF89 SYSREF 和 DACCLK 输入所需的最小差分输入电压。 数据表显示典型值为800mV、最大值为2000mV。 我知道 max 是输入差分电压不应超过的最高值、但这些输入所需的最低输入差分电压是多少、才能保证 DAC38RF89看到有效的输入开关转换?

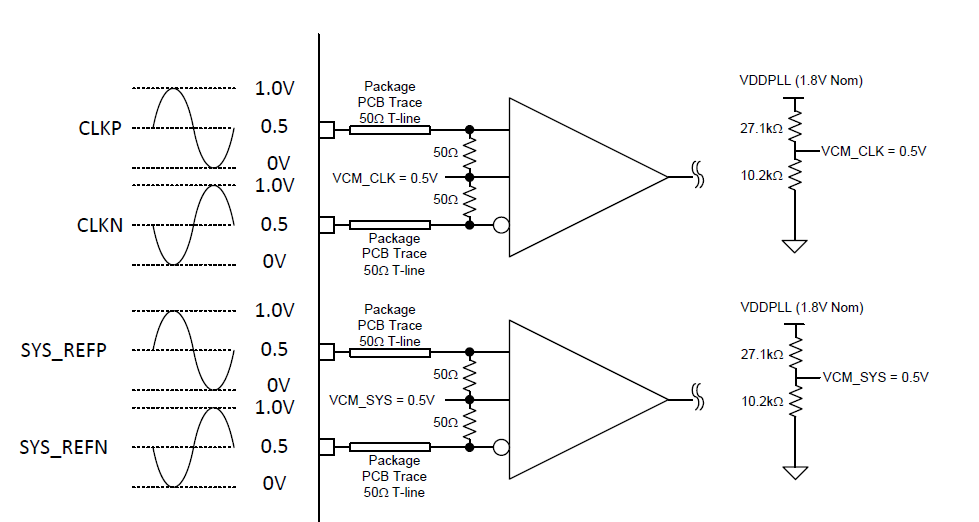

此外、共模电压列为0.5V 典型值。 时钟/SYSREF 驱动电路必须满足的最小/最大共模电压是多少? 对于时钟、可以进行交流耦合、但 SYSREF 不能直接进行交流耦合、因为它具有重要的直流分量。

谢谢!